### **EPROM Products**

1993/1994 Data Book/Handbook

Advanced Micro Devices

# **EPROM Products Data Book/Handbook**

1993/1994

### © 1993 Advanced Micro Devices, Inc.

Advanced Micro Devices reserves the right to make changes in its products without notice in order to improve design or performance characteristics.

This publication neither states nor implies any warranty of any kind, including but not limited to implied warrants of merchantability or fitness for a particular application. AMD® assumes no responsibility for the use of any circuitry other than the circuitry in an AMD product.

The information in this publication is believed to be accurate in all respects at the time of publication, but is subject to change without notice. AMD assumes no responsibility for any errors or omissions, and disclaims responsibility for any consequences resulting from the use of the information included herein. Additionally, AMD assumes no responsibility for the functioning of undescribed features or parameters.

#### Trademarks

AMD and the AMD logo are registered trademarks of Advanced Micro Devices, Inc.

ExpressROM, Flasherase and Flashrite are trademarks of Advanced Micro Devices, Inc.

Product names used in this publication are for identification purposes only and may be trademarks of their respective companies.

Advanced Micro Devices continues to be at the forefront of non-volatile memory technology. Our technology leadership is evidenced by the world's fastest and highest density EPROMs.

Our CMOS EPROM product portfolio is the broadest available. Today we offer EPROM densities ranging from 64K to 4 Megabit in both ceramic windowed and plastic one-time-programmable packages. Our superior EPROM process technology yields access times as fast as 35 ns enabling you to maximize system performance based on today's high speed microprocessors. Furthermore, we have expanded our product service by providing ExpressROM™ memories. These preprogrammed and fully tested devices provide users with a cost-effective alternative to EPROMs without the long lead-time associated with ROMs.

We are now proud to announce a family of true Low Voltage EPROMs to complement our product offering. Our low voltage product family consists of 1 Megabit and 2 Megabit devices with speeds of 120 ns and 150 ns respectively. The voltage range has been extended to make them suitable for systems that have regulated power supplies (3.0 V to 3.6 V) and those that are battery powered (2.7 V to 3.6 V). We have also expanded our package portfolio to include Thin Small Outline Packages (TSOP).

There has never been a better time to take advantage of AMD's family of non-volatile memories.

Walid Maghribi

Vice President and General Manager Non-Volatile Memory Division

įν

# **TABLE OF CONTENTS**

| Introduction | 1                             |                                                                          |            |

|--------------|-------------------------------|--------------------------------------------------------------------------|------------|

| Section 1    | Product Selec                 | ctor Guides                                                              | 1-1        |

|              |                               | PROM Memory Products                                                     | 1-3        |

|              |                               | P EPROMs                                                                 | 1-4        |

|              | ExpressRo                     | OM™ Memories                                                             | 1-7        |

| Section 2    |                               | ole Programmable Read Only Memories (EPROMs)                             | 2-1        |

|              | Inside AMD's                  | CMOS EPROM Technology                                                    | 2-3        |

|              | Am27C64                       | 64K (8,192 x 8-Bit) CMOS EPROM                                           | 2-10       |

|              | Am27C128                      | 128K (16,384 x 8-Bit) CMOS EPROM                                         | 2-22       |

|              | Am27C256                      | 256K (32,768 x 8-Bit) CMOS EPROM                                         | 2-34       |

|              | Am27C512                      | 512K (65,536 x 8-Bit) CMOS EPROM                                         | 2-47       |

|              | Am27C010                      | 1 Mbit (131,072 x 8-Bit) CMOS EPROM                                      | 2-59       |

|              | Am27C1024                     | 1 Mbit (65,536 x 16-Bit) CMOS EPROM                                      | 2-72       |

|              | Am27C020                      | 2 Mbit (262,144 x 8-Bit) CMOS EPROM                                      | 2-84       |

|              | Am27C2048                     | 2 Mbit (131,072 x 16-Bit) CMOS EPROM                                     | 2-96       |

|              | Am27C040                      | 4 Mbit (524,288 x 8-Bit) CMOS EPROM                                      | 2-109      |

|              | Am27C400                      | 4 Mbit (524,288 x 8-Bit/262,144 x 16-Bit) ROM Compatible CMOS EPROM      | 2-121      |

|              | Am27C4096                     | 4 Mbit (262,144 x 16-Bit) CMOS EPROM                                     | 2-133      |

|              | Am27C080                      | 8 Mbit (1,048,576 x 8-Bit) CMOS EPROM                                    | 2-145      |

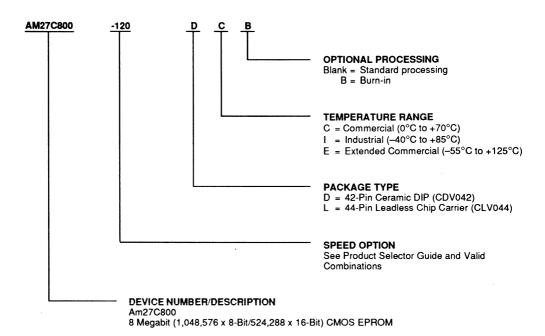

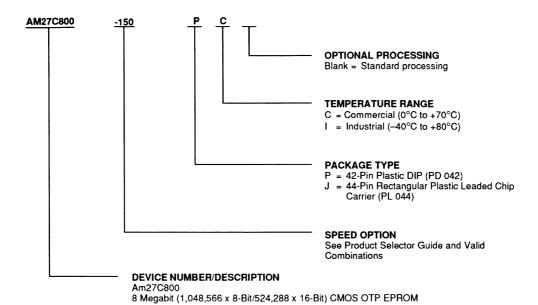

|              | Am27C800                      | 8 Mbit (1,048,576 x 8-Bit/524,288 x 16-Bit)<br>ROM Compatible CMOS EPROM | 2-157      |

| Section 3    | High-Speed C                  | MOS Erasable Programmable Read                                           | 0.4        |

|              |                               | n to High-Speed EPROMs                                                   | 3-1<br>3-3 |

|              | Am27H256                      | High-Speed 256K (32,768 x 8-Bit) CMOS EPROM                              | 3-3        |

|              | Am27H010                      | High-Speed 1 Mbit (131,072 x 8-Bit) CMOS EPROM                           | 3-21       |

|              |                               | , , , , , , , , , , , , , , , , , , , ,                                  | 3-21       |

| Section 4    | Low Voltage (<br>Only Memorie | CMOS Erasable Programmable Read s (EPROMs)                               | 4-1        |

|              |                               | n to Low Voltage EPROMs                                                  | 4-3        |

|              | Am27LV010/                    | 1 Mbit (131,072 x 8-Bit) Low Voltage                                     | 7-3        |

|              | Am27LV010B                    | CMOS EPROM                                                               | 4-4        |

|              | Am27LV020/<br>Am27LV020B      | 2 Mbit (262,144 x 8-Bit) Low Voltage CMOS EPROM                          | 4-21       |

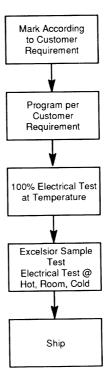

| Section 5    | ExpressROM <sup>T</sup>       | Memories                                                                 | 5-1        |

|              |                               | to ExpressROM Memories                                                   | 5-3        |

|              | Am27X64                       | 64K (8,192 x 8-Bit) CMOS ExpressROM Device                               | 5-8        |

|              | Am27X128                      | 128K (16,384 x 8-Bit) CMOS ExpressROM Device                             | 5-17       |

|              | Am27X256                      | 256K (32,768 x 8-Bit) CMOS ExpressROM Device                             | 5-26       |

|              | Am27X512                      | 512K (65,536 x 8-Bit) CMOS ExpressROM Device                             | 5-36       |

|              | Am27X010                      | 1 Mbit (131,072 x 8-Bit) CMOS ExpressROM Device                          | 5-45       |

|              |                               | •                                                                        |            |

| Section 5 | ExpressROM <sup>TI</sup> | Memories (continued)                                                            |       |

|-----------|--------------------------|---------------------------------------------------------------------------------|-------|

|           | Am27X1024                | 1 Mbit (65,536 x 16-Bit) CMOS ExpressROM Device                                 | 5-55  |

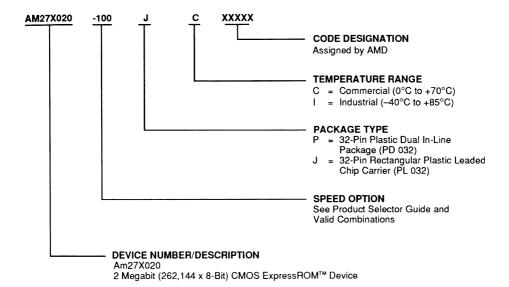

|           | Am27X020                 | 2 Mbit (262,144 x 8-Bit) CMOS ExpressROM Device                                 | 5-64  |

|           | Am27X2048                | 2 Mbit (131,072 x 16-Bit) CMOS ExpressROM Device                                | 5-73  |

|           | Am27X040                 | 4 Mbit (524,288 x 8-Bit) CMOS ExpressROM Device                                 | 5-82  |

|           | Am27X400                 | 4 Mbit (524,288 x 8-Bit/262,144 x 16-Bit) ROM Compatible ExpressROM Device      | 5-91  |

|           | Am27X4096                | 4 Mbit (262,144 x 16-Bit) CMOS ExpressROM Device                                | 5-100 |

|           | Am27X080                 | 8 Mbit (1,048,576 x 8-Bit) CMOS ExpressROM Device                               | 5-109 |

|           | Am27X800                 | 8 Mbit (1,048,576 x 8-Bit/524,288 x 16-Bit)<br>ROM Compatible ExpressROM Device | 5-118 |

| Section 6 | Programming              |                                                                                 | 6-1   |

|           |                          | Methodology                                                                     | 6-3   |

|           |                          | amming Flowchart                                                                | 6-4   |

|           | -                        | ng Characteristics                                                              | 6-5   |

|           |                          | cteristics and Waveforms                                                        | 6-5   |

|           |                          | gramming Support                                                                | 6-9   |

| Section 7 | Article Reprin           | t                                                                               | 7-1   |

|           | "Making EPRO             | M/Flash Trade-Offs" Article Reprint                                             | 7-3   |

| Section 8 | Physical Dime            | ensions                                                                         | 8-1   |

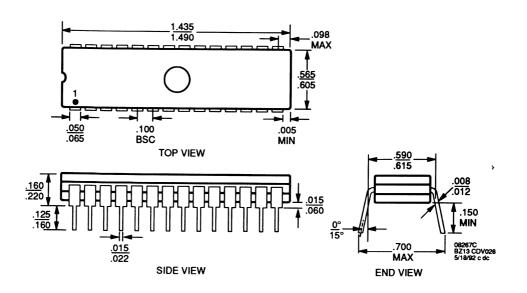

|           | CDV028                   | 28-Pin Ceramic DIP                                                              | 8-3   |

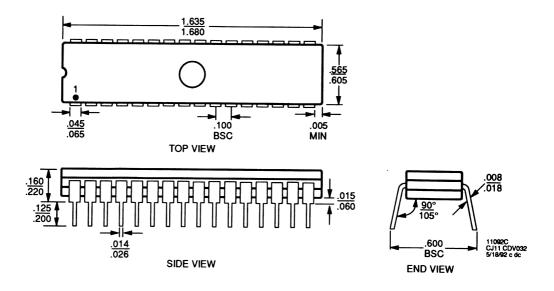

|           | CDV032                   | 32-Pin Ceramic DIP                                                              | 8-3   |

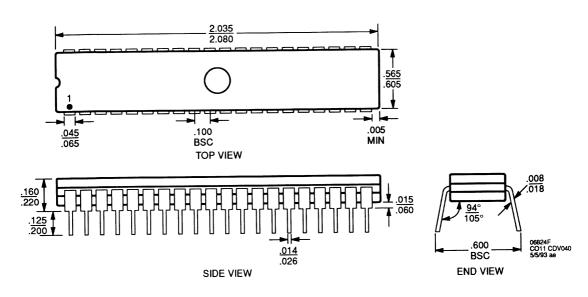

|           | CDV040                   | 40-Pin Ceramic DIP                                                              | 8-4   |

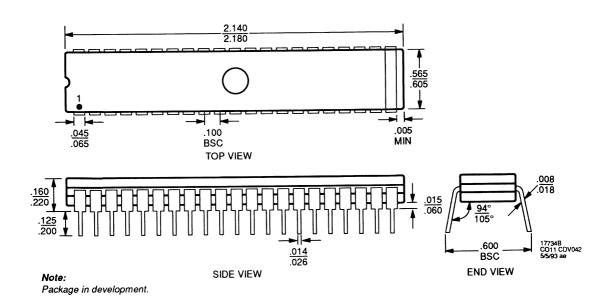

|           | CDV042                   | 42-Pin Ceramic DIP                                                              | 8-4   |

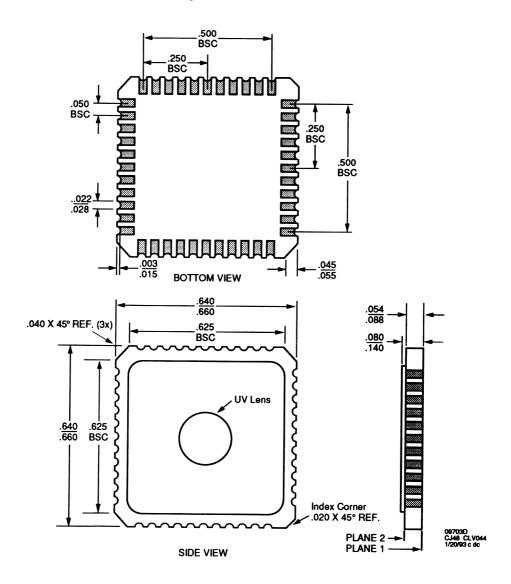

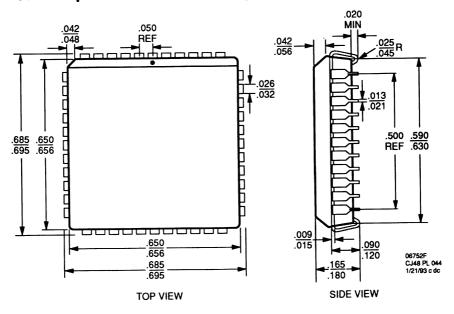

|           | CLV044                   | 44-Pin Square Leadless Chip Carrier                                             | 8-5   |

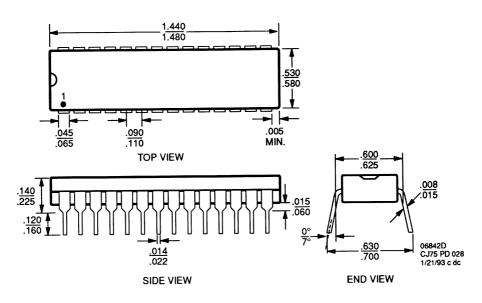

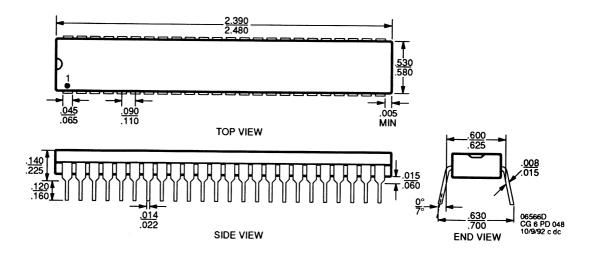

|           | PD 028                   | 28-Pin Plastic Dual In-Line Package                                             | 8-6   |

|           | PD 032                   | 32-Pin Plastic Dual In-Line Package                                             | 8-6   |

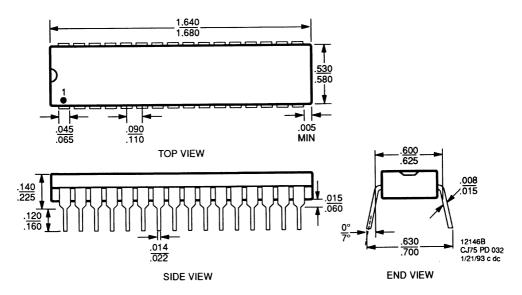

|           | PD 040                   | 40-Pin Plastic Dual In-Line Package                                             | 8-7   |

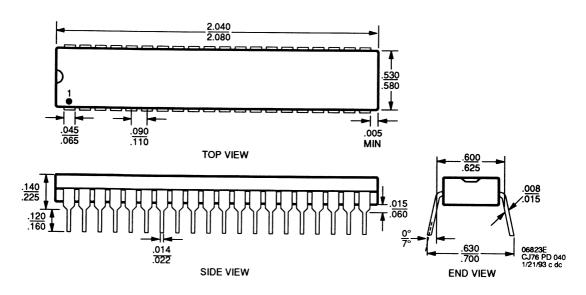

|           | PD 048                   | 48-Pin Plastic Dual In-Line Package                                             | 8-7   |

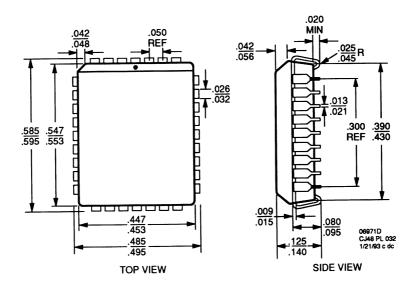

|           | PL 032                   | 32-Pin Rectangular Plastic Leaded Chip Carrier                                  | 8-8   |

|           | PL 044                   | 44-Pin Rectangular Plastic Leaded Chip Carrier                                  | 8-8   |

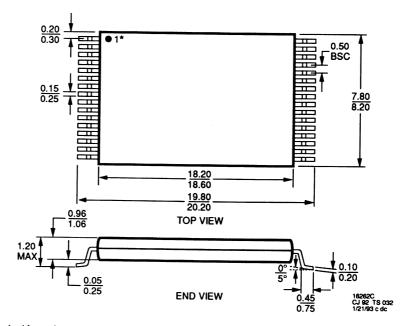

|           | TS 032                   | 32-Pin Thin Small Outline                                                       | 8-9   |

# SECTION

# PRODUCT SELECTOR GUIDES

| Section 1 | Product Selector Guides            | 1-1 |

|-----------|------------------------------------|-----|

|           | Non-Volatile EPROM Memory Products | 1-3 |

|           | UV & OTP EPROMs                    | 1-4 |

|           | ExpressROM <sup>TM</sup> Memories  | 1.7 |

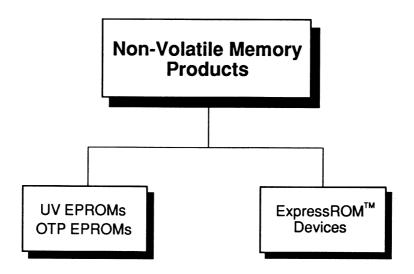

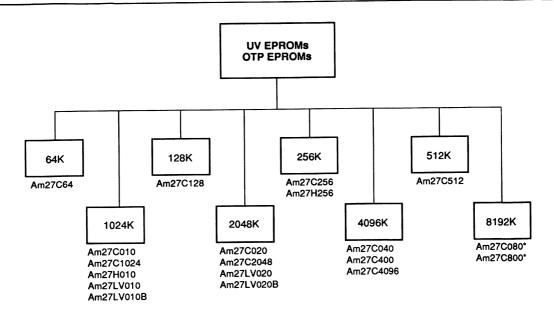

# **Non-Volatile EPROM Memory Products**

#### Introduction

The Non-Volatile Memory Division manufactures a broad range of high performance memory products. These products include traditional windowed EPROMs, plastic OTP EPROMs, and ExpressROM devices. They offer the system designer an extensive choice of economical alternatives for program storage.

AMD's EPROM offerings are manufactured using advanced CMOS process technology yielding access times as fast as 35 ns. Product densities range from 64K to 4 megabits. Designers challenged with extending useful battery life in portable applications will appreciate the 3 Volt EPROM product family. All EPROM products are offered in windowed ceramic and One-Time Programmable (OTP) plastic packages.

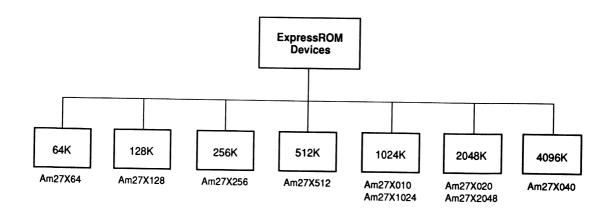

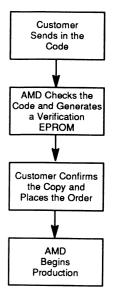

A new concept from AMD is the ExpressROM device. These are quick-turn ROMs produced from EPROM wafers. Lead times of these devices are typically half that of ROMs.

AMD is committed to leadership in high-performance CMOS non-volatile memories. These products offer industry-leading speeds and densities that will contribute to the competitive advantages of your design.

#### **UV EPROMS & OTP EPROMS**

| Part<br>Number | Organization | Access<br>Time (ns) | Temp<br>Range¹ | Package<br>Type² | Pin Count<br>(DIP/PLCC)<br>(TSOP) | Supply<br>Voltage |

|----------------|--------------|---------------------|----------------|------------------|-----------------------------------|-------------------|

| Am27C64-55     | 8K x 8       | 55                  | С              | D, L             | 28/32                             | 5 V ± 5%          |

| Am27C64-70     | 8K x 8       | 70                  | C              | D, L             | 28/32                             | 5 V ± 10%         |

| Am27C64-90     | 8K x 8       | 90                  | C, I, E, M     | D, L, P, J       | 28/32                             | 5 V ± 10%         |

| Am27C64-120    | 8K x 8       | 120                 | C, I, E, M     | D, L, P, J       | 28/32                             | 5 V ± 10%         |

| Am27C64-150    | 8K x 8       | 150                 | C, I, E, M     | D, L, P, J       | 28/32                             | 5 V ± 10%         |

| Am27C64-200    | 8K x 8       | 200                 | C, I, E, M     | D, L, P, J       | 28/32                             | 5 V ± 10%         |

| Am27C64-255    | 8K x 8       | 250                 | C, I           | D, L, P, J       | 28/32                             | 5 V ± 5%          |

| Am27C128-55    | 16K x 8      | 55                  | c              | D. L             | 28/32                             | 5 V ± 5%          |

| Am27C128-70    | 16K x 8      | 70                  | Č              | D, L             | 28/32                             | 5 V ± 10%         |

| Am27C128-90    | 16K x 8      | 90                  | C, I, E, M     | D, L, P, J       | 28/32                             | 5 V ± 10%         |

| Am27C128-120   | 16K x 8      | 120                 | C, I, E, M     | D, L, P, J       | 28/32                             | 5 V ± 10%         |

| Am27C128-150   | 16K x 8      | 150                 | C, I, E, M     | D, L, P, J       | 28/32                             | 5 V ± 10%         |

| Am27C128-200   | 16K x 8      | 200                 | C, I, E, M     | D, L, P, J       | 28/32                             | 5 V ± 10%         |

| Am27C128-255   | 16K x 8      | 250                 | C, I           | D, L, P, J       | 28/32                             | 5 V ± 5%          |

| Am27H256-35    | 32K x 8      | 35                  | c              | D, L             | 28/32                             | 5 V ± 10%         |

| Am27H256-35V05 | 32K x 8      | 35                  | C              | D. L             | 28/32                             | 5 V ± 5%          |

| Am27H256-45    | 32K x 8      | 45                  | C, I, E, M     | D, L, P, J       | 28/32                             | 5 V ± 10%         |

| Am27H256-55    | 32K x 8      | 55                  | C, I, E, M     | D, L, P, J       | 28/32                             | 5 V ± 10%         |

| Am27H256-70    | 32K x 8      | 70                  | C, I, E, M     | D, L, P, J       | 28/32                             | 5 V ± 10%         |

| Am27C256-55    | 32K x 8      | 55                  | c              | D, L             | 28/32                             | 5 V ± 5%          |

| Am27C256-70    | 32K x 8      | 70                  | Č              | D, L             | 28/32                             | 5 V ± 10%         |

| Am27C256-90    | 32K x 8      | 90                  | Č, I, E, M     | D, L, P, J, E    | 28/32                             | 5 V ± 10%         |

| Am27C256-120   | 32K x 8      | 120                 | C, I, E, M     | D, L, P, J, E    | 28/32                             | 5 V ± 10%         |

| Am27C256-150   | 32K x 8      | 150                 | C, I, E, M     | E                | 28/32                             | 5 V ± 10%         |

| Am27C256-200   | 32K x 8      | 200                 | C, I, E, M     | D, L, P, J, E    | 28/32                             | 5 V ± 10%         |

| Am27C256-255   | 32K x 8      | 250                 | C, i           | D, L, P, J       | 28/32                             | 5 V ± 5%          |

#### UV EPROMs & OTP EPROMs (Cont.)

| Part<br>Number | Organization | Access<br>Time (ns) | Temp<br>Range¹ | Package<br>Type <sup>2</sup> | Pin Count<br>(DIP/PLCC)<br>(TSOP) | Supply<br>Voltage              |

|----------------|--------------|---------------------|----------------|------------------------------|-----------------------------------|--------------------------------|

| Am27C512-75    | 64K x 8      | 70                  | С              | D, L                         | 28/32                             | 5 V ± 5%                       |

| Am27C512-90    | 64K x 8      | 90                  | C, I, E, M     | D. L                         | 28/32                             | 5 V ± 10%                      |

| Am27C512-120   | 64K x 8      | 120                 | C, I, E, M     | D. L                         | 28/32                             | 5 V ± 10%                      |

| Am27C512-150   | 64K x 8      | 150                 | C, I, E, M     | D, L, P, J                   | 28/32                             | 5 V ± 10%                      |

| Am27C512-200   | 64K x 8      | 200                 | C, I, E, M     | D, L, P, J                   | 28/32                             | 5 V ± 10%                      |

| Am27C512-255   | 64K x 8      | 250                 | C, I, E, M     | D, L, P, J                   | 28/32                             | 5 V ± 5%                       |

| Am27H010-45    | 128K x 8     | 45                  | c              | D, L                         | 32/32                             | 5 V ± 10%                      |

| Am27H010-45V05 | 128K x 8     | 45                  | l C            | D, L                         | 32/32                             | 5 V ± 5%                       |

| Am27H010-55    | 128K x 8     | 55                  | C, I, E, M     | D, L, P, J                   | 32/32                             | 5 V ± 10%                      |

| Am27H010-70    | 128K x 8     | 70                  | C. I. E. M     | D, L, P, J                   | 32/32                             | 5 V ± 10%                      |

| Am27H010-90    | 128K x 8     | 90                  | C, I, E, M     | D, L, P, J                   | 32/32                             | 5 V ± 10%                      |

| Am27H010-90V05 | 128K x 8     | 90                  | C, I, E, M     | D, L, P, J                   | 32/32                             | 5 V ± 5%                       |

| Am27C010-105   | 128K x 8     | 100                 | С              | D. L                         | 32/32                             | 5 V ± 5%                       |

| Am27C010-120   | 128K x 8     | 120                 | C, I           | D. L. P. J. E                | 32/32                             | 5 V ± 10%                      |

| Am27C010-150   | 128K x 8     | 150                 | C, I, E, M     | D, L, P, J, E                | 32/32                             | 5 V ± 10%                      |

| Am27C010-200   | 128K x 8     | 200                 | C, I, E, M     | D, L, P, J, E                | 32/32                             | 5 V ± 10%                      |

| Am27C010-255   | 128K x 8     | 250                 | C, I           | D, L, P, J, E                | 32/32                             | 5 V ± 5%                       |

| Am27LV010-120  | 128K x 8     | 120                 | C, I, E        | D, L                         | 32                                | 3.3 V ± 10%                    |

| Am27LV010-150  | 128K x 8     | 150                 | C, I, E, M     | D. L. J. E                   | 32                                | 3.3 V ± 10%                    |

| Am27LV010-200  | 128K x 8     | 200                 | C, I, E, M     | D, L, J, E                   | 32                                | 3.3 V ± 10%                    |

| Am27LV010-250  | 128K x 8     | 250                 | C, I, E, M     | D, L, J, E                   | 32                                | 3.3 V ± 10%                    |

| Am27LV010-300  | 128K x 8     | 300                 | C, I, E, M     | D, L, J, E                   | 32                                | 3.3 V ± 10%                    |

| Am27LV010B-150 | 128K x 8     | 150                 | C, I, E        | D. L. J. E                   | 32                                | 2.7 V - 3.6 V                  |

| Am27LV010B-200 | 128K x 8     | 200                 | C, i, E        | D, L, J, E                   | 32                                | 2.7 V = 3.6 V                  |

| Am27LV010B-250 | 128K x 8     | 250                 | C, I, E, M     | D, L, J, E                   | 32                                | 2.7 V = 3.6 V                  |

| Am27LV010B-300 | 128K x 8     | 300                 | C, I, E, M     | D, L, J, E                   | 32                                | 2.7 V – 3.6 V                  |

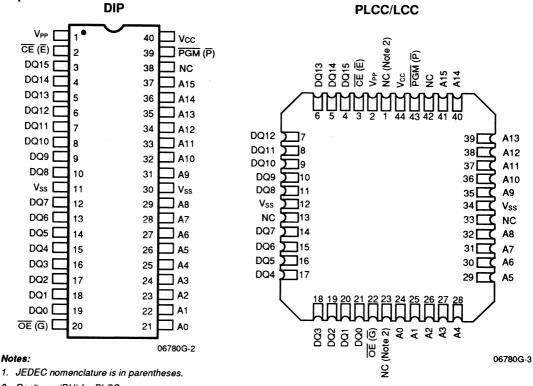

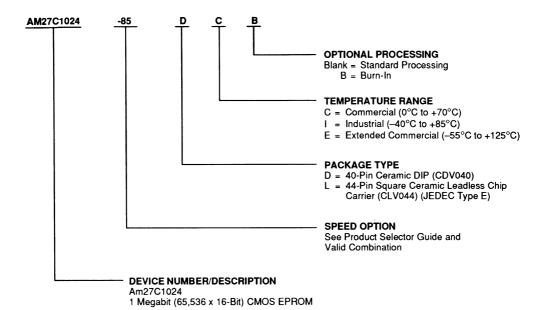

| Am27C1024-85   | 64K x 16     | 85                  | С              | D                            | 40                                | 5 V ± 5%                       |

| Am27C1024-90   | 64K x 16     | 90                  | C. I           | D. L                         | 40/44                             | 5 V ± 10%                      |

| Am27C1024-120  | 64K x 16     | 120                 | C, I, E, M     | D.L                          | 40/44                             | 5 V ± 10%                      |

| Am27C1024-150  | 64K x 16     | 150                 | C, I, E, M     | D, L                         | 40/44                             | 5 V ± 10%                      |

| Am27C1024-200  | 64K x 16     | 200                 | C, I, E, M     | D, L, P, J                   | 40/44                             | 5 V ± 10%                      |

| Am27C1024-255  | 64K x 16     | 250                 | C, i           | D, L, P, J                   | 40/44                             | 5 V ± 5%                       |

| Am27C020-120   | 256K x 8     | 120                 | C, I           | D, L                         | 32/32                             | 5 V ± 10%                      |

| Am27C020-150   | 256K x 8     | 150                 | C, I, E, M     | D, L, P, J*                  | 32/32                             | 5 V ± 10%                      |

| Am27C020-200   | 256K x 8     | 200                 | C, I, E, M     | D, L, P, J*                  | 32/32                             | 5 V ± 10%                      |

| Am27C020-250   | 256K x 8     | 250                 | M              | D, L.                        | 32/32                             | 5 V ± 10%                      |

| Am27C020-255   | 256K x 8     | 250                 | C, I           | D, L, P, J*                  | 32/32                             | 5 V ± 5%                       |

| Am27LV020-150  | 256K x 8     | 150                 | C, I, E        | D, L, J                      | 32                                | 3.3 V ± 10%                    |

| Am27LV020-200  | 256K x 8     | 200                 | C, I, E, M     | D, L, 3                      | 32<br>32                          |                                |

| Am27LV020-250  | 256K x 8     | 250                 | C, I, E, M     | D, L, J                      | 32<br>32                          | 3.3 V ± 10%                    |

| Am27LV020-300  | 256K x 8     | 300                 | C, I, E, M     | D, L, J                      | 32<br>32                          | 3.3 V ± 10%<br>3.3 V ± 10%     |

| Am27LV020B-200 | 128K x 8     | 200                 | C, I, E        | D, L, J                      | 32                                | 2.7 V – 3.6 V                  |

| Am27LV020B-250 | 128K x 8     | 250                 | C, İ, E, M     | D, L, J                      | 32                                | 2.7 V = 3.6 V<br>2.7 V = 3.6 V |

| Am27LV020B-300 | 128K x 8     | 300                 | C, I, E, M     | D, L, J                      | 32                                | 2.7 V – 3.6 V<br>2.7 V – 3.6 V |

| Am27C2048-105* | 128K x 16    | 100                 | С              | D, L                         | 40/44                             | 5 V ± 5%                       |

| Am27C2048-120  | 128K x 16    | 120                 | Č. I           | D, L                         | 40/44                             | 5 V ± 10%                      |

| Am27C2048-150  | 128K x 16    | 150                 | Č, İ, E, M     | D, L, P, J                   | 40/44                             | 5 V ± 10%   5 V ± 10%          |

| Am27C2048-200  | 128K x 16    | 200                 | C, I, E, M     | D, L, P, J                   | 40/44                             | 5 V ± 10%<br>5 V ± 10%         |

| Am27C2048-250  | 128K x 16    | 250                 | M, E, W        | D, L, 1, 3                   | 40/44                             |                                |

|                | 128K x 8     | 250                 | Ö, ı           | D, L, P, J                   | 40/44                             | 5 V ± 10%                      |

#### UV EPROMs & OTP EPROMs (Cont.)

| Part<br>Number                                                                               | Organization                                                                                               | Access<br>Time (ns)                    | Temp<br>Range¹                                | Package<br>Type²                                         | Pin Count<br>(DIP/PLCC)<br>(TSOP)                  | Supply<br>Voltage                                                        |

|----------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|----------------------------------------|-----------------------------------------------|----------------------------------------------------------|----------------------------------------------------|--------------------------------------------------------------------------|

| Am27C040-120<br>Am27C040-125<br>Am27C040-150<br>Am27C040-200<br>Am27C040-250<br>Am27C040-255 | 512K x 8<br>512K x 8<br>512K x 8<br>512K x 8<br>512K x 8<br>512K x 8<br>512K x 8                           | 120<br>120<br>150<br>200<br>250<br>250 | C, I<br>C, I, E, M<br>C, I, E, M<br>M<br>C, I | D, L<br>D, L<br>D, L<br>D, L, P, J<br>D, L<br>D, L, P, J | 32/32<br>32/32<br>32/32<br>32/32<br>32/32<br>32/32 | 5 V ± 10%<br>5 V ± 5%<br>5 V ± 10%<br>5 V ± 10%<br>5 V ± 10%<br>5 V ± 5% |

| Am27C400-125<br>Am27C400-120<br>Am27C400-150<br>Am27C400-200<br>Am27C400-255                 | 512K x 8/256K x 16<br>512K x 8/256K x 16<br>512K x 8/256K x 16<br>512K x 8/256K x 16<br>512K x 8/256K x 16 | 120<br>120<br>150<br>200<br>250        | C, I<br>C, I<br>C, I                          | D<br>D<br>D<br>D                                         | 40<br>40<br>40<br>40<br>40                         | 5 V ± 5%<br>5 V ± 10%<br>5 V ± 10%<br>5 V ± 10%<br>5 V ± 5%              |

| Am27C4096-125                                                                                | 256K x 16                                                                                                  | 120                                    | C, I                                          | D, L                                                     | 40/44                                              | 5 V ± 5%                                                                 |

| Am27C4096-120                                                                                | 256K x 16                                                                                                  | 120                                    | C, I                                          | D, L                                                     | 40/44                                              | 5 V ± 10%                                                                |

| Am27C4096-150                                                                                | 256K x 16                                                                                                  | 150                                    | C, I, E, M                                    | D, L, P, J                                               | 40/44                                              | 5 V ± 10%                                                                |

| Am27C4096-200                                                                                | 256K x 16                                                                                                  | 200                                    | C, I, E, M                                    | D, L, P, J                                               | 40/44                                              | 5 V ± 10%                                                                |

| Am27C4096-250                                                                                | 256K x 16                                                                                                  | 250                                    | M                                             | D, L                                                     | 40/44                                              | 5 V ± 10%                                                                |

| Am27C4096-255                                                                                | 256K x 16                                                                                                  | 250                                    | C, I                                          | D, L, P, J                                               | 40/44                                              | 5 V ± 5%                                                                 |

| Am27C080-105*                                                                                | 1 Megabit x 8                                                                                              | 100                                    | C, I                                          | D, L                                                     | 32/32                                              | 5 V± 5%                                                                  |

| Am27C080-120*                                                                                | 1 Megabit x 8                                                                                              | 120                                    | C, I                                          | D, L                                                     | 32/32                                              | 5 V± 10%                                                                 |

| Am27C080-150*                                                                                | 1 Megabit x 8                                                                                              | 150                                    | C, I, E, M                                    | D, L, P, J                                               | 32/32                                              | 5 V± 10%                                                                 |

| Am27C080-200*                                                                                | 1 Megabit x 8                                                                                              | 200                                    | C, I, E, M                                    | D, L, P, J                                               | 32/32                                              | 5 V± 10%                                                                 |

| Am27C080-250*                                                                                | 1 Megabit x 8                                                                                              | 250                                    | M                                             | D, L                                                     | 32/32                                              | 5 V± 10%                                                                 |

| Am27C080-255*                                                                                | 1 Megabit x 8                                                                                              | 250                                    | C, I                                          | D, L, P, J                                               | 32/32                                              | 5 V± 5%                                                                  |

| Am27C800-125*                                                                                | 1 Megabit x 8/512K x 16                                                                                    | 120                                    | C, I                                          | D, L                                                     | 42/44                                              | 5 V ± 5%                                                                 |

| Am27C800-120*                                                                                | 1 Megabit x 8/512K x 16                                                                                    | 120                                    | C, I                                          | D, L                                                     | 42/44                                              | 5 V ± 10%                                                                |

| Am27C800-150*                                                                                | 1 Megabit x 8/512K x 16                                                                                    | 150                                    | C, I, E, M                                    | D, L, P, J                                               | 42/44                                              | 5 V ± 10%                                                                |

| Am27C800-200*                                                                                | 1 Megabit x 8/512K x 16                                                                                    | 200                                    | C, I, E, M                                    | D, L, P, J                                               | 42/44                                              | 5 V ± 10%                                                                |

| Am27C800-250*                                                                                | 1 Megabit x 8/512K x 16                                                                                    | 250                                    | M                                             | D, L                                                     | 42/44                                              | 5 V ± 10%                                                                |

| Am27C800-255*                                                                                | 1 Megabit x 8/512K x 16                                                                                    | 250                                    | C, I                                          | D, L, P, J                                               | 42/44                                              | 5 V ± 5%                                                                 |

<sup>\*</sup>Contact the local AMD sales office for the availability of this device.

#### **ExpressROM Devices**

| Part<br>Number               | Organization | Access<br>Time (ns) | Temp<br>Range¹ | Package<br>Type <sup>2</sup> | Pin Count<br>(PDIP/PLCC) | Supply<br>Voltage |

|------------------------------|--------------|---------------------|----------------|------------------------------|--------------------------|-------------------|

| Am27X64-90                   | 8K x 8       | 90                  | C, I           | P, J                         | 28/32                    | <b>511.</b> 1011  |

| Am27X64-120                  | 8K x 8       | 120                 | С, I           | P, J                         |                          | 5 V ± 10%         |

| Am27X64-150                  | 8K x 8       | 150                 | c, i           | P, J                         | 28/32                    | 5 V ± 10%         |

| Am27X64-200                  | 8K x 8       | 200                 | C, i           | P, J                         | 28/32                    | 5 V ± 10%         |

| Am27X64-255                  | 8K x 8       | 250                 | C, I.          | P. J                         | 28/32<br>28/32           | 5 V ± 10%         |

|                              |              |                     | <b>-,</b>      | 1,0                          | 20/32                    | 5 V ± 5%          |

| Am27X128-90                  | 16K x 8      | 90                  | C, I           | P, J                         | 28/32                    | 5 V ± 10%         |

| Am27X128-120                 | 16K x 8      | 120                 | C, I           | P, J                         | 28/32                    | 5 V ± 10%         |

| Am27X128-150                 | 16K x 8      | 150                 | Ċ, i           | P, J                         | 28/32                    | 5 V ± 10%         |

| Am27X128-200                 | 16K x 8      | 200                 | C, I           | P, J                         | 28/32                    | 5 V ± 10%         |

| Am27X128-255                 | 16K x 8      | 250                 | C, I           | P, J                         | 28/32                    | 5 V± 10%          |

| Am27X256-90                  | 32K x 8      |                     |                |                              |                          | 0.11 0.0          |

| Am27X256-120                 | 32K x 8      | 90                  | C, I           | P, J                         | 28/32                    | 5 V ± 10%         |

| Am27X256-150                 | 32K x 8      | 120                 | C, I           | P, J                         | 28/32                    | 5 V ± 10%         |

| Am27X256-200                 |              | 150                 | C, I           | P, J                         | 28/32                    | 5 V ± 10%         |

| Am27X256-255                 | 32K x 8      | 200                 | C, I           | P, J                         | 28/32                    | 5 V ± 10%         |

| AIII27 A230-233              | 32K x 8      | 250                 | С, І           | P, J                         | 28/32                    | 5 V ± 5%          |

| Am27XH256-45                 | 32K x 8      | 45                  | C, I           | P, J                         | 00.00                    |                   |

| Am27XH256-55                 | 32K x 8      | 55                  | C, i           | P, J                         | 28/32                    | 5 V ± 10%         |

| Am27XH256-70                 | 32K x 8      | 70                  | č, i           | P, J                         | 28/32<br>28/32           | 5 V ± 10%         |

|                              |              |                     | ٥, ١           | 1,5                          | 26/32                    | 5 V ± 10%         |

| Am27X512-90                  | 64K x 8      | 90                  | C, I           | P, J                         | 28/32                    | 5 V ± 10%         |

| Am27X512-120                 | 64K x 8      | 120                 | C, I           | P, J                         | 28/32                    | 5 V ± 10%         |

| Am27X512-150                 | 64K x 8      | 150                 | C, I           | P, J                         | 28/32                    | 5 V ± 10%         |

| Am27X512-200                 | 64K x 8      | 200                 | C, I           | P, J                         | 28/32                    | 5 V ± 10%         |

| Am27X512-255                 | 64K x 8      | 250                 | C, I           | P, J                         | 28/32                    | 5 V ± 10%         |

| Am27X010-105                 | 128K x 8     | 105                 |                |                              |                          | 3 7 1 3 %         |

| Am27X010-105<br>Am27X010-120 | 128K X 8     | 105                 | C, !           | P, J                         | 32/32                    | 5 V ± 5%          |

| Am27X010-120<br>Am27X010-150 |              | 120                 | C, I           | P, J                         | 32/32                    | 5 V ± 10%         |

| Am27X010-150<br>Am27X010-200 | 128K x 8     | 150                 | C, I           | P, J                         | 32/32                    | 5 V ± 10%         |

| Am27X010-200<br>Am27X010-255 | 128K x 8     | 200                 | C, I           | P, J                         | 32/32                    | 5 V ± 10%         |

| AIII2/AU10-205               | 128K x 8     | 250                 | C, I           | P, J                         | 32/32                    | 5 V ± 5%          |

| Am27XH010-55                 | 128K x 8     | 55                  | C, I           | P. J                         | 20.00                    |                   |

| Am27XH010-70                 | 128K x 8     | 70                  | c, i           |                              | 32/32                    | 5 V ± 10%         |

| Am27XH010-90                 | 128K x 8     | 90                  | C, i           | P, J<br>P, J                 | 32/32                    | 5 V ± 10%         |

| es: see page 1-8             |              |                     | 0, 1           | F, J                         | 32/32                    | 5 V ± 10%         |

#### **ExpressROM Devices (Cont.)**

| Part<br>Number                                                   | Organization                                                  | Access<br>Time (ns)      | Temp<br>Range¹               | Package<br>Type <sup>2</sup> | Pin Count<br>(PDIP/PLCC)         | Supply<br>Voltage                               |

|------------------------------------------------------------------|---------------------------------------------------------------|--------------------------|------------------------------|------------------------------|----------------------------------|-------------------------------------------------|

| Am27X1024-120<br>Am27X1024-150<br>Am27X1024-200<br>Am27X1024-255 | 64K x 16<br>64K x 16<br>64K x 16<br>64K x 16                  | 120<br>150<br>200<br>250 | C, I<br>C, I<br>C, I         | P, J<br>P, J<br>P, J<br>P, J | 40/44<br>40/44<br>40/44<br>40/44 | 5 V ± 10%<br>5 V ± 10%<br>5 V ± 10%<br>5 V ± 5% |

| Am27X020-125<br>Am27X020-150<br>Am27X020-200<br>Am27X020-255     | 256K x 8<br>256K x 8<br>256K x 8<br>256K x 8                  | 125<br>150<br>200<br>250 | C, I<br>C, I<br>C, I<br>C, I | P<br>P<br>P                  | 32/32<br>32/32<br>32/32<br>32/32 | 5 V ± 10%<br>5 V ± 10%<br>5 V ± 10%<br>5 V ± 5% |

| Am27X2048-125<br>Am27X2048-150<br>Am27X2048-200<br>Am27X2048-255 | 128K x 16<br>128K x 16<br>128K x 16<br>128K x 16<br>128K x 16 | 120<br>150<br>200<br>250 | C, I<br>C, I<br>C, I<br>C, I | P, J<br>P, J<br>P, J<br>P, J | 40/44<br>40/44<br>40/44<br>40/44 | 5 V ± 10%<br>5 V ± 10%<br>5 V ± 10%<br>5 V ± 5% |

| Am27X040-150<br>Am27X040-200                                     | 512K x 8<br>512K x 8                                          | 150<br>200               | C, I<br>C, I                 | P, J<br>P, J                 | 32/32<br>32/32                   | 5 V ± 10%<br>5 V ± 10%                          |

#### Notes:

- 1. Temperature Range

- C = Commercial (0°C to 70°C)

- I = Industrial (-40°C to +85°C)

- E = Extended Commercial (-55°C to +125°C)

- M = Military (-55°C to +125°C) most products available in both APL and DESC versions.

#### 2. Package Type

- D = Ceramic DIP

- L = Rectangular Ceramic Leadless Chip Carrier

- P = Plastic DIP

- J = Rectangular Plastic Leaded Chip Carrier

- E = Thin Small Outline Package standard pin-out

- F = Thin Small Outline Package reverse pin-out

### SECTION

# 2 CMOS ERASABLE PROGRAMMABLE READ ONLY MEMORIES (EPROMs)

| Section 2 | CMOS Erasable Programmable Read Only Memories (EPROMs) 2-1 |                                             |  |  |  |  |  |

|-----------|------------------------------------------------------------|---------------------------------------------|--|--|--|--|--|

|           | Inside AMD's                                               | CMOS EPROM Technology 2-3                   |  |  |  |  |  |

|           | Am27C64                                                    | 64K (8,192 x 8-Bit) CMOS EPROM 2-10         |  |  |  |  |  |

|           | Am27C128                                                   | 128K (16,384 x 8-Bit) CMOS EPROM 2-22       |  |  |  |  |  |

|           | Am27C256                                                   | 256K (32,768 x 8-Bit) CMOS EPROM 2-34       |  |  |  |  |  |

|           | Am27C512                                                   | 512K (65,536 x 8-Bit) CMOS EPROM 2-47       |  |  |  |  |  |

|           | Am27C010                                                   | 1 Mbit (131,072 x 8-Bit) CMOS EPROM 2-59    |  |  |  |  |  |

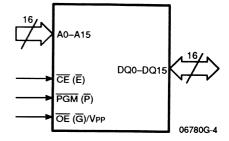

|           | Am27C1024                                                  | 1 Mbit (65,536 x 16-Bit) CMOS EPROM 2-72    |  |  |  |  |  |

|           | Am27C020                                                   | 2 Mbit (262,144 x 8-Bit) CMOS EPROM 2-84    |  |  |  |  |  |

|           | Am27C2048                                                  | 2 Mbit (131,072 x 16-Bit) CMOS EPROM 2-96   |  |  |  |  |  |

|           | Am27C040                                                   | 4 Mbit (524,288 x 8-Bit) CMOS EPROM 2-109   |  |  |  |  |  |

|           | Am27C400                                                   | 4 Mbit (524,288 x 8-Bit/262,144 x 16-Bit)   |  |  |  |  |  |

|           |                                                            | ROM Compatible CMOS EPROM 2-121             |  |  |  |  |  |

|           | Am27C4096                                                  | 4 Mbit (262,144 x 16-Bit) CMOS EPROM 2-133  |  |  |  |  |  |

|           | Am27C080                                                   | 8 Mbit (1,048,576 x 8-Bit) CMOS EPROM 2-145 |  |  |  |  |  |

|           | Am27C800                                                   | 8 Mbit (1,048,576 x 8-Bit/524,288 x 16-Bit) |  |  |  |  |  |

|           |                                                            | ROM Compatible CMOS EPROM 2-157             |  |  |  |  |  |

# INSIDE AMD'S CMOS EPROM TECHNOLOGY

#### **TECHNOLOGY DESCRIPTION**

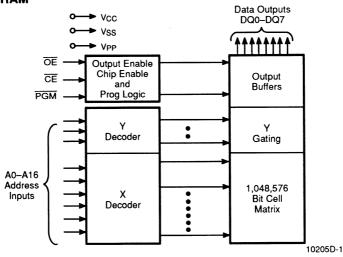

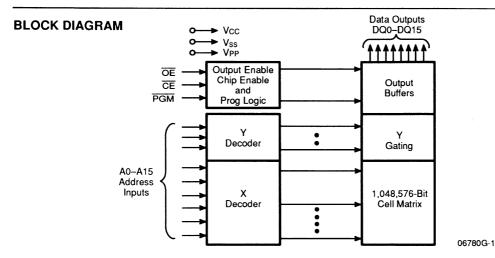

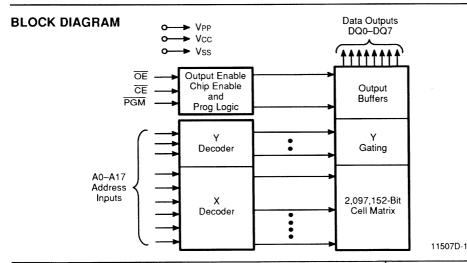

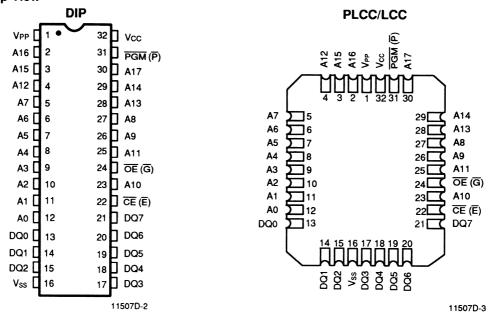

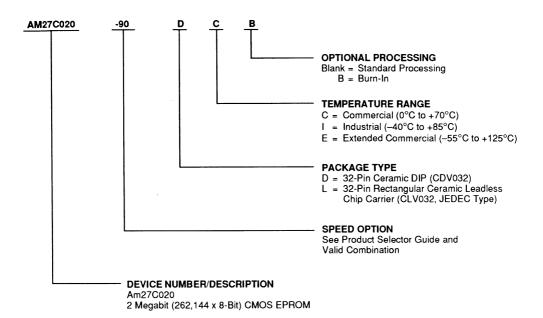

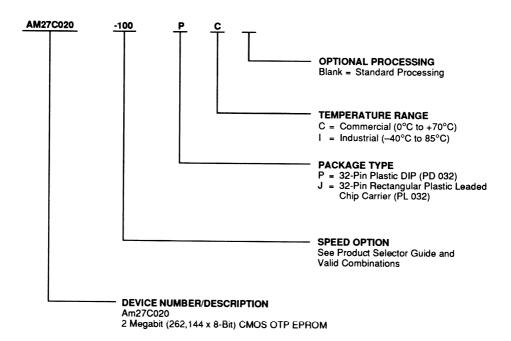

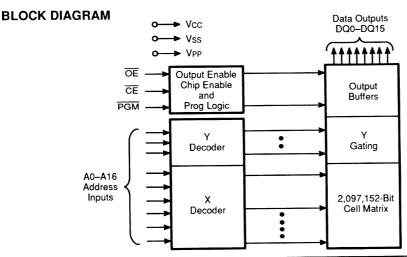

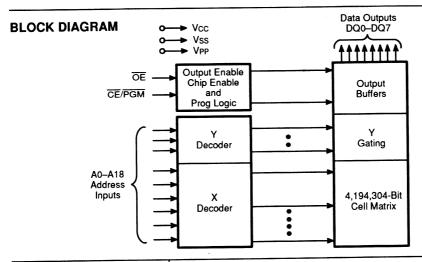

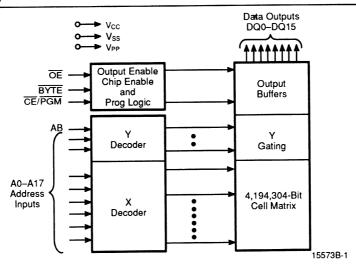

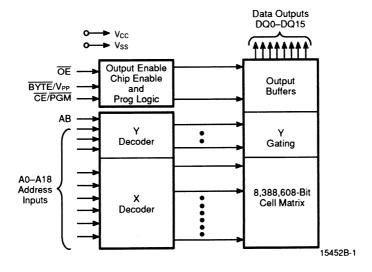

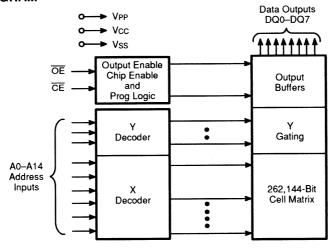

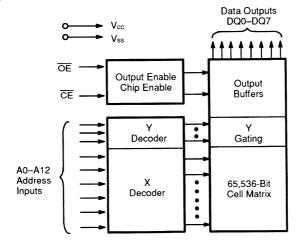

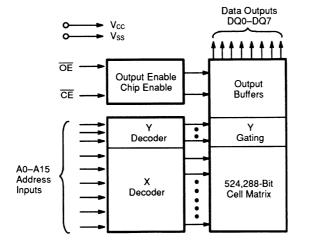

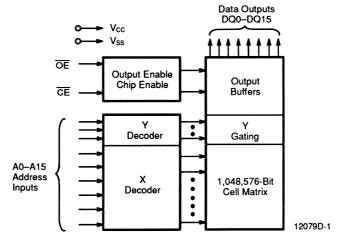

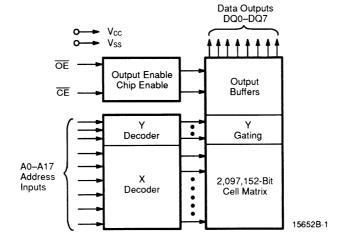

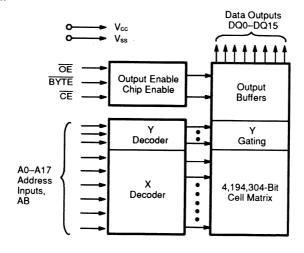

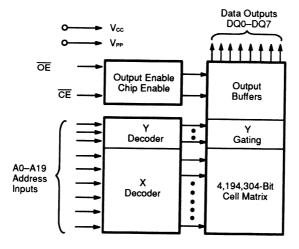

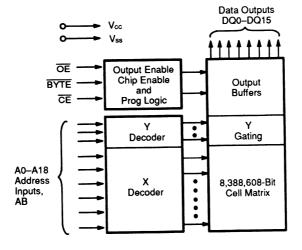

AMD's CMOS EPROM memories use standard CMOS periphery with an n-channel floating-gate memory array. The output buffers of the devices are designed to be compatible with both TTL and CMOS circuits. An n-channel pull-down and a p-channel pull-up provide full rail-to-rail switching of the outputs. The CMOS technology also allows very low standby power dissipation: 1.0 mA maximum TTL standby and 100 µA maximum CMOS standby currents.

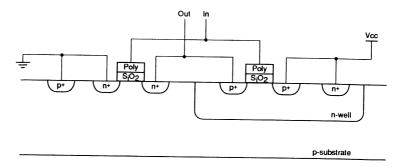

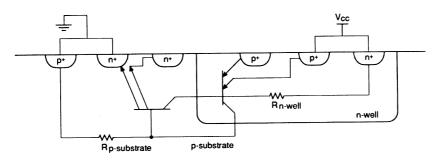

Figure 1 shows a cross-section of a basic inverter. The gates consist of polysilicon; the other connections are made with metal. The technology used for the periphery transistors is CMOS (Complementary MOS) technology which combines n and p channel devices on the same silicon. In this case, a non-epitaxial p-type substrate is used for the n-channel transistors and a deep diffused n-well is used for the p-channel transistors.

The fabrication of CMOS EPROM memories is a complex process where every step must be rigorously monitored and controlled. This complex processing is heavily dependent on the following underlying technologies:

#### **Photolithography**

The photo or masking technology is key to the manufacturing of integrated circuits (ICs). It allows the same circuits to be printed hundreds of times on the same wafer. It is also inherent to the patterning of the various structures on the wafer necessary to the fabrication of the ICs. Today, with the improved capability of wafer steppers, AMD's EPROM products are manufactured on geometries of one micron and below.

Figure 2-1 CMOS Inverter Cross-Section

17061A-1

#### Ion Implantation

lon implantation provides precision dopant control that is so critical for the manufacturing of AMD's EPROM products on sub-micron technology. Ion implantation equipment is a combination of mass spectrometry, linear acceleration, high resolution, current integration, ion beam scanning and high vacuum technologies. This process uses charged dopant atoms that are accelerated by an electric field and are implanted into the silicon wafer at a depth determined by the acceleration energy.

#### Diffusion

The furnace operations are required for silicon oxidation and driving in dopants. Oxidation cycles are used to grow the gate and isolation oxides inherent to the fabrication and operation of the MOS transistors. Drive cycles are used to diffuse the dopant material into the silicon to give the desired profile and depth.

#### Thin Films

Thin films deposited on the silicon include: polysilicon for gate electrodes and interconnection, interlayer dielectrics, metal layers for interconnection and passivation layers to seal the topside.

#### **AMD EPROM Technology**

The manufacturing technology for AMD's EPROM products involves a complex combination and blending of the previously mentioned processes. Each processing step requires a tremendous level of development, optimization and control. Before any new product is put into manufacturing, it must satisfy AMD's commitment to customer satisfaction, quality and reliability. To meet these standards, every new process and new product must pass many rigorous requirements. These requirements are outlined in greater depth in the reliability section.

The AMD EPROM products are being built on the CS19/19A family of technologies. These technologies are all based on a double-poly, single-metal n-well CMOS process. This process has been optimized for high density as well as high performance non-volatile memory devices. The basic features of this family of technologies are:

- n-well CMOS

- non-epitaxial, grounded substrate

- double-poly, single-metal

|                              | CS19 | CS19A |

|------------------------------|------|-------|

| minimum feature (microns)    | 1.0  | 0.85  |

| gate length (Leff) (microns) | 0.9  | 0.7   |

| gate oxide (Angstrom)        | 190  | 190   |

| contacts (microns)           | 1.0  | 0.85  |

| metal pitch (microns)        | 3.0  | 2.7   |

#### **CS19**

This is a 1.0  $\mu m$  minimum feature conventional technology and is used to manufacture the low density and high speed EPROM products offered by AMD.

#### CS19A

This is an 0.85  $\mu m$  minimum feature conventional technology and is used to manufacture the medium to high density EPROM products and the family of low voltage EPROM products offered by AMD.

#### **UV-ERASABLE TECHNOLOGY**

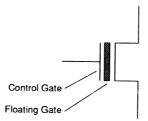

AMD's CMOS EPROM technology is based upon the concept of stored charge. The charge is stored on a floating gate, that is a gate that has no connection to the rest of the circuit. The storage transistor actually has two gates: one that floats, and the other that acts as a control gate. The control gate is used to establish the field across the floating gate (see Figure 2).

Figure 2-2 Floating-Gate MOS Transistor

17061A-2

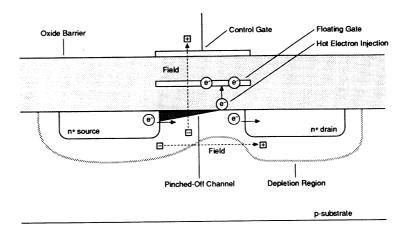

Hot electron injection is used for programming EPROM devices. With this scheme, a bias is set up between the source and drain of the transistor, and between the control gate and the substrate (see Figure 3). The channel is pinched off, and a strong current flows. Because of the high fields, the electrons are hot. The two fields (source-to-drain, and substrate-to-control-gate) combine to form a field in a diagonal direction, but because of the oxide barrier, electrons cannot flow in that direction. Occasionally, electrons acquire enough energy to cross the barrier in the shortest direction—from the channel to the floating gate. This is referred to as hot electron injection.

Once an electron is on the other side of the oxide, it is on the floating gate, with no conductive path to get off. It is therefore effectively trapped and remains there. During programming, large fields are set up so that a significant number of electrons are injected.

Erasing these devices requires exposure to ultraviolet light. The energy from the ultraviolet light causes the electrons to cross back over the oxide barrier thereby erasing the device. For this to happen, the device package must have a window that lets the ultraviolet light pass through.

The program and erase mechanisms of all of AMD's EPROM products are fundamentally identical irrespective of the type of technology (CS19 or CS19A) used.

Figure 2-3 Programming by Hot-Electron Injection

17061A-3

#### **Erasing AMD EPROMs**

In order to clear all locations of their programmed contents, it is necessary to expose the EPROM to an ultraviolet light source. A dosage of 15 W sec/cm² is required to completely erase an EPROM. This dosage can be obtained by exposure to an ultraviolet lamp—wavelength of 2537 Å—with intensity of 12,000  $\mu\text{W/cm}^2$  for 15 to 20 minutes. The EPROM should be directly under and about one inch from the source and all filters should be removed from the UV light source prior to erasure.

It is important to note that the EPROM, and similar devices, will erase with light sources having wavelengths shorter than 4000 Å, although erasure times will be much longer than with UV sources at 2537 Å. Nevertheless, the exposure to fluorescent light and sunlight will eventually erase the EPROM and exposure to them should be prevented to realize maximum system reliability. If used in such an environment, the package window should be covered by an opaque label or substance.

#### **Programming AMD EPROMs**

Upon delivery, or after each erasure, the EPROM has all bits in the "ONE," or HIGH state. "Zeros" are loaded into the EPROM through the procedure of programming.

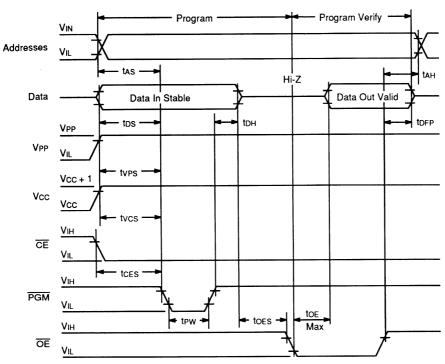

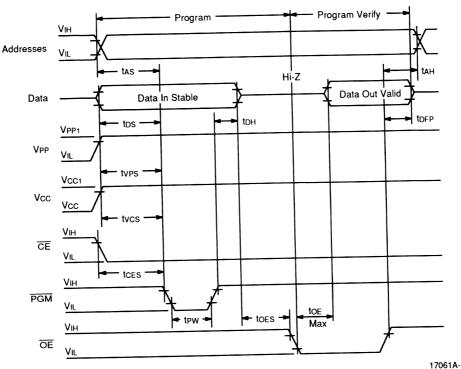

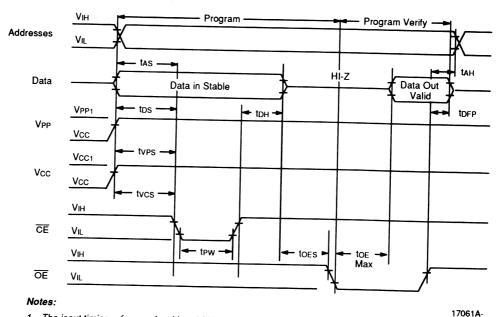

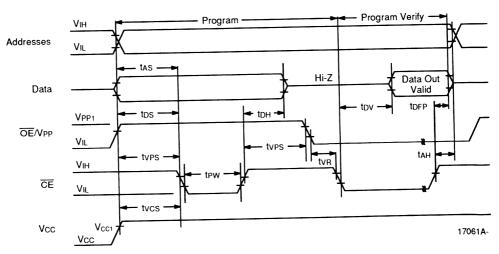

The programming mode is entered when 12.75 V  $\pm$  0.25 V is applied to the V<sub>PP</sub> pin,  $\overline{\text{CE}}$  is at V<sub>IL</sub> and  $\overline{\text{OE}}$  is at V<sub>IH</sub>. For programming, the data to be programmed is applied in parallel to the data input-output pins.

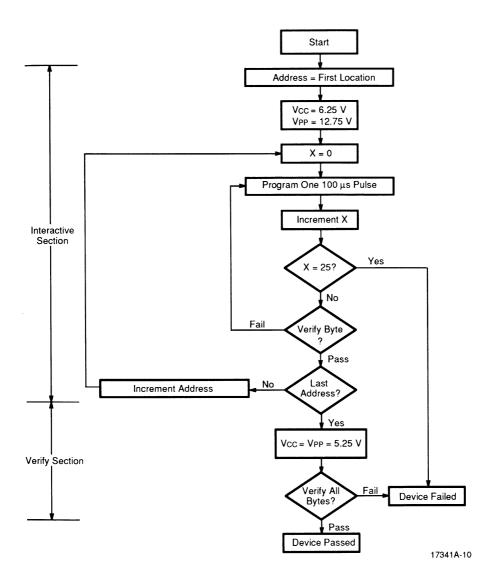

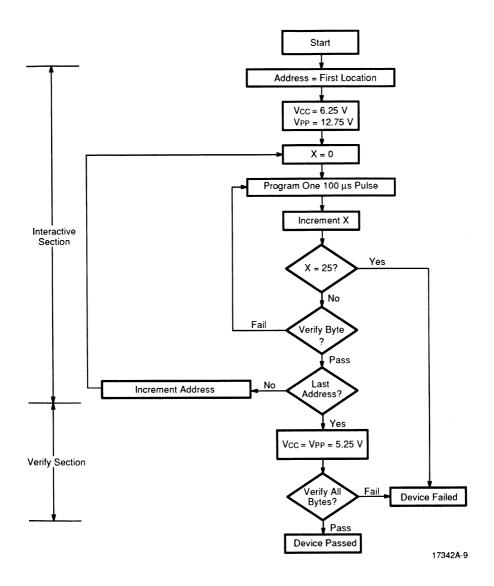

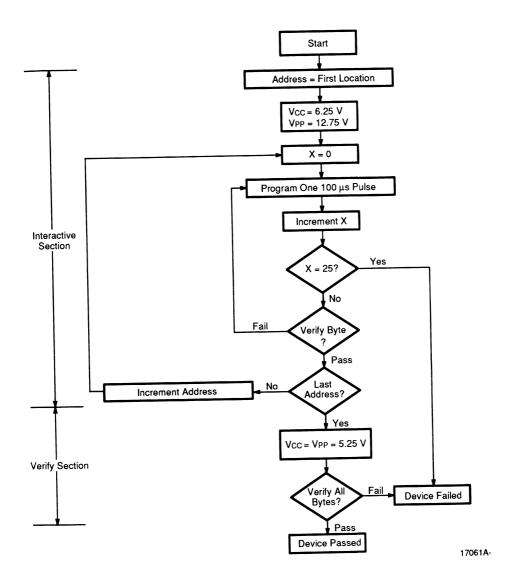

The Flashrite<sup>™</sup> programming algorithm reduces programming time by using an initial 100 µs pulse followed by a byte verification operation to determine whether the byte has been successfully programmed. If the data does not verify, an additional pulse is applied for up to a maximum of 25 pulses. This process is repeated while sequencing through each address of the EPROM.

The Flashrite programming algorithm programs and verifies at  $V_{CC}=6.25~V$  and  $V_{PP}=12.75~V$ . After the final address is completed, all bytes are compared to the original data with  $V_{CC}=V_{PP}=5.25~V$ .

#### **ESD**

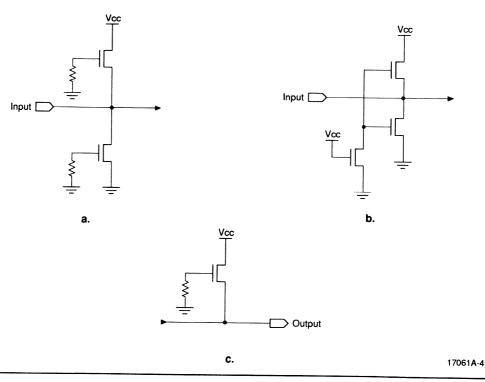

Every pin on the device is protected against electrostatic discharge (ESD), a formal name for static electricity shocks. Output pins rely on the large output drivers as protection. Inputs normally do not have large drivers, so a circuit must be added for input protection. In addition to ESD protection, these input protection circuits also help provide clamping against negative overshoot.

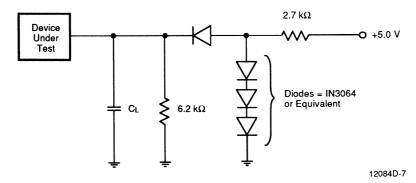

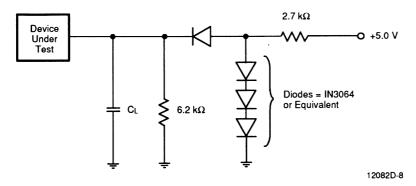

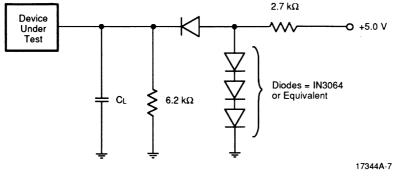

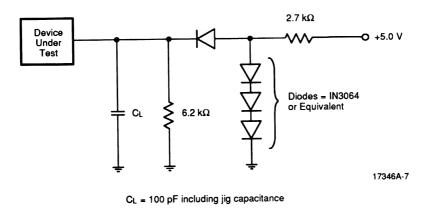

AMD CMOS EPROMs make use of ESD protection circuits as shown in Figures 4a through 4c. Most input pins use the circuit in Figure 4b. On output pins the ESD protection circuit has been modified as shown in Figure 4c.

Figure 2-4 ESD Protection: a. New Version; b. Standard; c. Output Pins

#### Latch-Up

All of AMD's CMOS devices are guaranteed to endure a current pulse of 100 mA into or out of the pin without inducing latch-up; most devices can actually withstand over 200 mA. Since AMD's CMOS EPROMs have true CMOS outputs, hot insertion is not recommended.

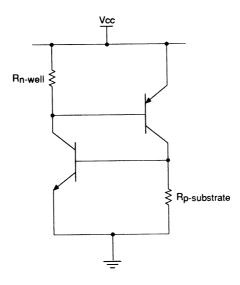

Latch-up may occur as a result of parasitic bipolar transistors between the n-channel and p-channel devices (see Figure 5a). These transistors form a parasitic Silicon Control Rectifier (SCR) (see Figure 5b), which turns ON when triggered, conducting large amounts of current. It is usually impossible to shut OFF without removing all the power from the device. The amount of current drain is so high that it can either overload

a power supply or, if the power supply can supply huge amounts of current, destroy the device.

Latch-up is normally triggered by an input or output at a voltage significantly above  $V_{\rm CC}$  or below ground, with enough current drawn to cause the SCR to turn on. This condition usually occurs when hot-socketing a part; i.e., plugging a part into a powered-up board or inserting a board into a powered-up system. When this happens, the inputs and  $V_{\rm CC}$  power up uncontrolled, and there is a risk of latch-up.

For CMOS outputs, the SCR is an intrinsic part of the CMOS structure and cannot be eliminated. The SCR must be made as difficult as possible to turn ON by using guard rings and very carefully laying out input and output circuits.

Figure 2-5 Latch-Up Mechanism: a. Cross-Section; b. Equivalent Schematic

a.

b.

17061A-5

#### **System Applications**

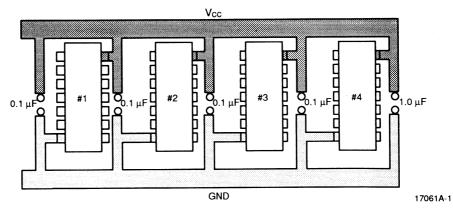

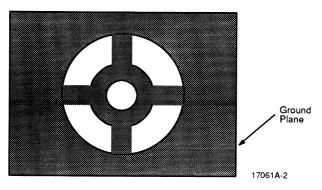

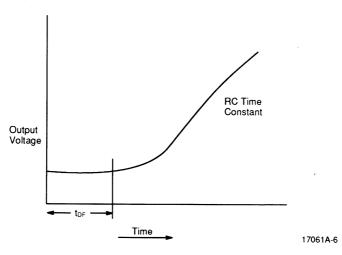

During the switch between active and standby conditions, transient current peaks are produced on the rising and falling edges of Chip Enable. The magnitude of these transient current peaks is dependent on the output capacitance loading of the device. At a minimum, a 0.1  $\mu F$  ceramic capacitor (high frequency, low inherent inductance) should be used on each device between  $V_{CC}$  and GND to minimize transient effects. In addition, to overcome the voltage drop caused by the inductive effects of the printed circuit board traces on EPROM arrays, a 4  $\mu F$  bulk electrolytic capacitor should be used between  $V_{CC}$  and GND for every eight devices. The location of the capacitor should be as close to where the power supply is connected to the array.

#### SUMMARY

By concentrating on the needs of CMOS users, AMD has developed industry-leading CMOS technology that can provide cost-effective EPROMs of unsurpassed quality, reliability and performance. AMD provides value through:

- Robust technology and circuit design which

- Does not generate high current transients, and

- Has high immunity to system noise

- An extremely broad offering of products:

- 64K through 4 Mbit commodity EPROM densities

- High-speed family with access times as fast as 35 ns

- Low-voltage products

- Regulated (3.0 V 3.6 V)

- Unregulated (2.7 V − 3.6 V)

This note has detailed many of the aspects of the technology that make it superior to other alternatives. This, together with the information in the individual data sheets, qualification books, and a crew of applications engineers, should provide answers to your questions as you make use of AMD's CMOS EPROM technology.

# Advanced Micro Devices

# Am27C64

### 64 Kilobit (8,192 x 8-Bit) CMOS EPROM

#### **DISTINCTIVE CHARACTERISTICS**

- Fast access time

- 45 ns

- Low power consumption

- 20 µA typical CMOS standby current

- **■** JEDEC-approved pinout

- Single +5 V power supply

- **■** ±10% power supply tolerance available

- 100% Flashrite<sup>TM</sup> programming

- Typical programming time of 1 second

- Latch-up protected to 100 mA from -1 V to Vcc + 1 V

- High noise immunity

- Versatile features for simple interfacing

- Both CMOS and TTL input/output compatibility

- Two line control functions

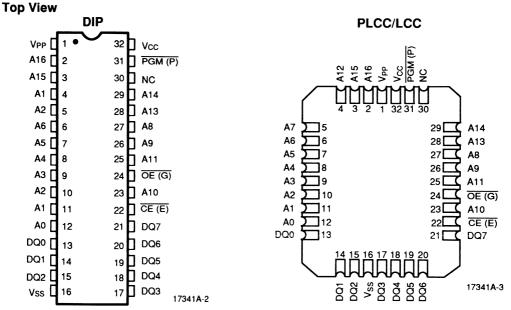

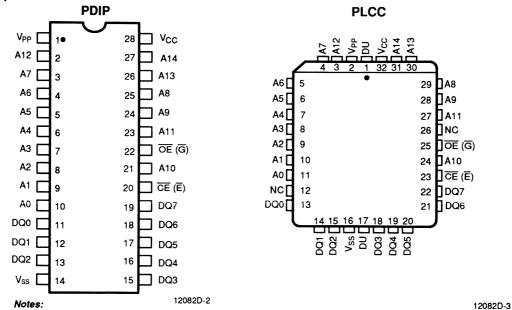

- Standard 28-pin DIP, PDIP, 32-pin LCC and PLCC packages

#### **GENERAL DESCRIPTION**

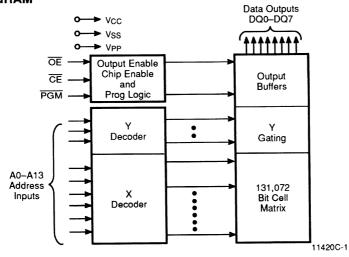

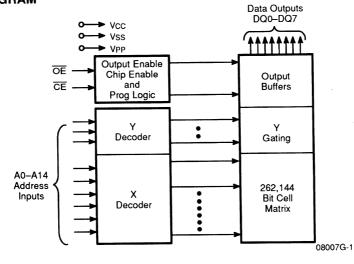

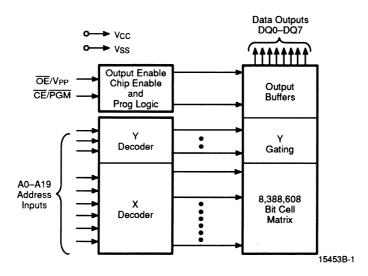

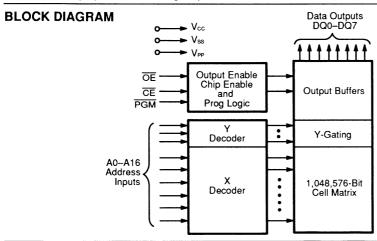

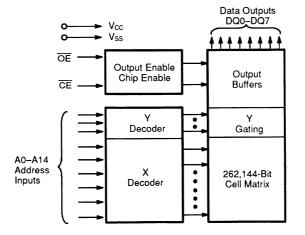

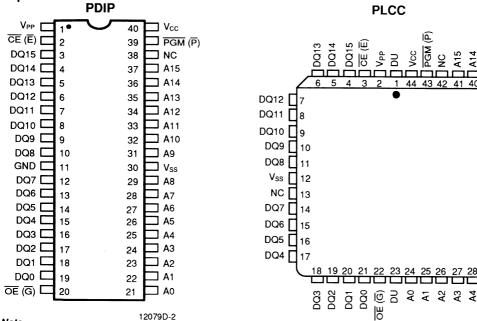

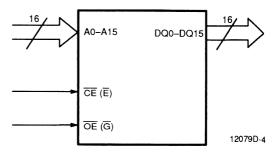

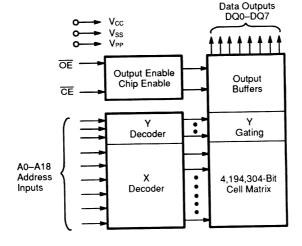

The Am27C64 is a 64-Kbit ultraviolet erasable programmable read-only memory. It is organized as 8K words by 8 bits per word, operates from a single +5 V supply, has a static standby mode, and features fast single address location programming. Products are available in windowed ceramic DIP and LCC packages as well as plastic one time programmable (OTP) PDIP, and PLCC packages.

Typically, any byte can be accessed in less than 45 ns, allowing operation with high-performance microprocessors without any WAIT states. The Am27C64 offers separate Output Enable ( $\overline{OE}$ ) and Chip Enable ( $\overline{CE}$ )

controls, thus eliminating bus contention in a multiple bus microprocessor system.

AMD's CMOS process technology provides high speed, low power, and high noise immunity. Typical power consumption is only 80 mW in active mode, and 100  $\mu W$  in standby mode.

All signals are TTL levels, including programming signals. Bit locations may be programmed singly, in blocks, or at random. The Am27C64 supports AMD's Flashrite™ programming algorithm (100 µs pulses) resulting in a typical programming time of 1 second.

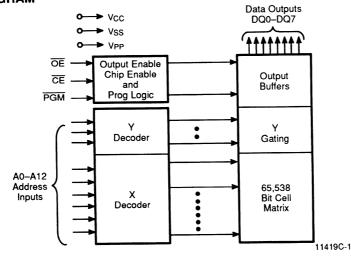

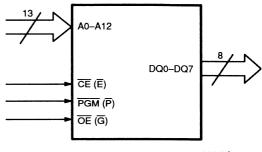

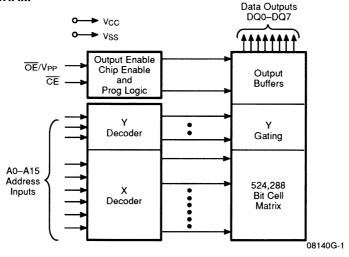

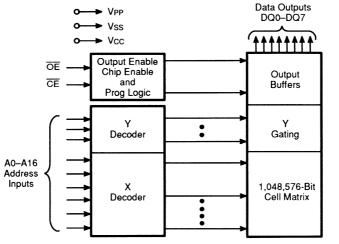

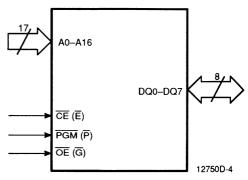

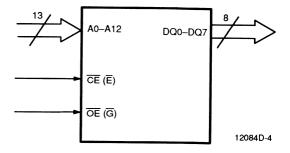

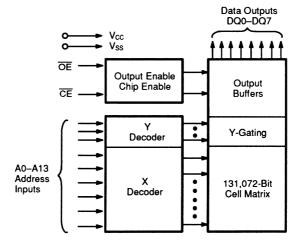

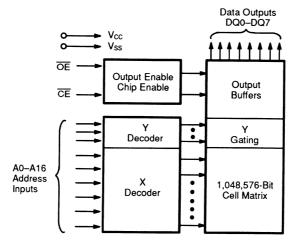

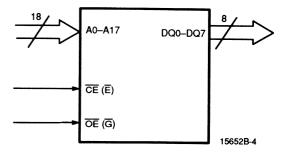

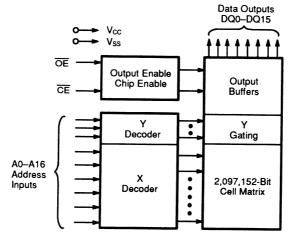

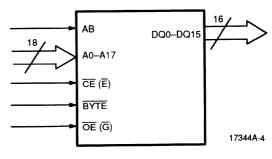

#### **BLOCK DIAGRAM**

Publication# 11419 Rev. C Amendment/0 Issue Date: July 1993

#### PRODUCT SELECTOR GUIDE

| Family Part No.               | Am27C64 |     |     |     |      |      |      |      |

|-------------------------------|---------|-----|-----|-----|------|------|------|------|

| Ordering Part No:<br>Vcc ± 5% |         |     |     |     |      |      |      | -255 |

| Vcc ± 10%                     | -45     | -55 | -70 | -90 | -120 | -150 | -200 | -250 |

| Max Access Time (ns)          | 45      | 55  | 70  | 90  | 120  | 150  | 200  | 250  |

| CE (E) Access Time (ns)       | 45      | 55  | 70  | 90  | 120  | 150  | 200  | 250  |

| OE (G) Access Time (ns)       | 30      | 35  | 40  | 40  | 50   | 65   | 75   | 100  |

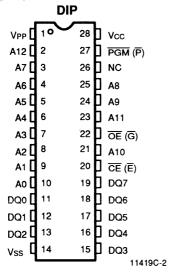

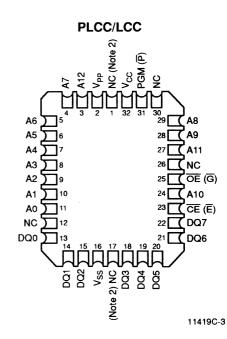

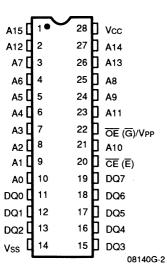

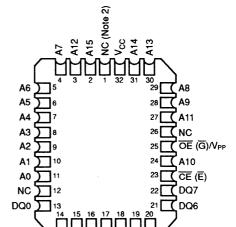

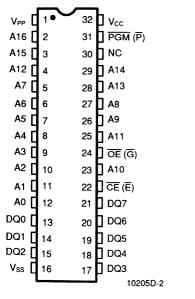

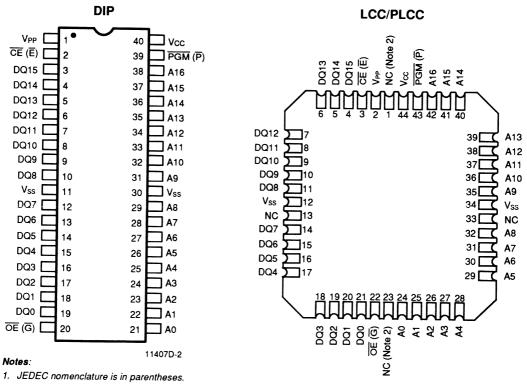

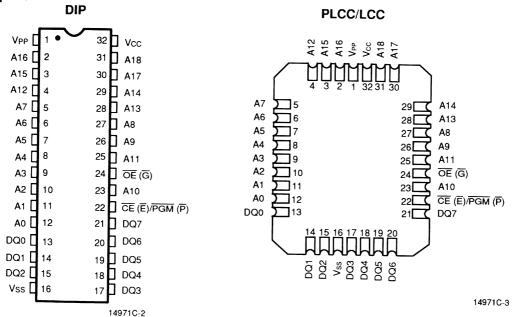

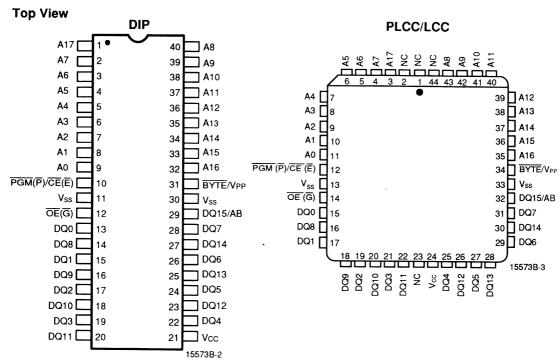

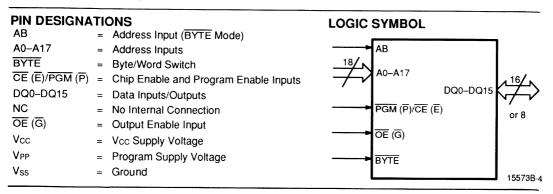

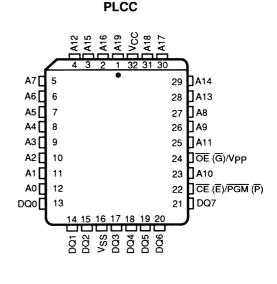

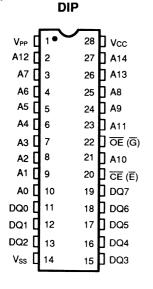

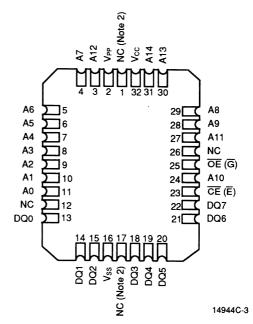

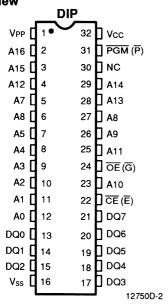

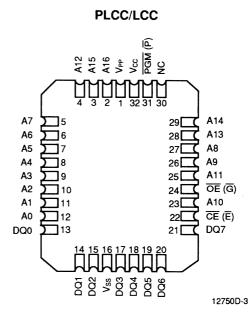

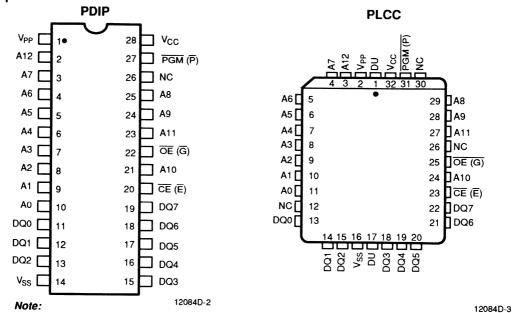

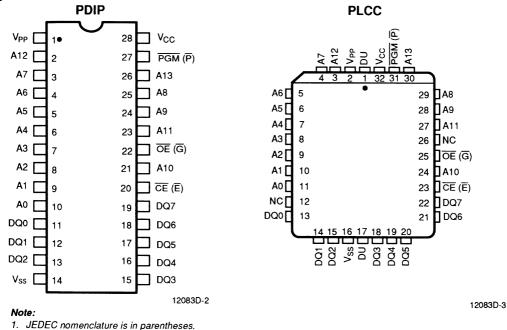

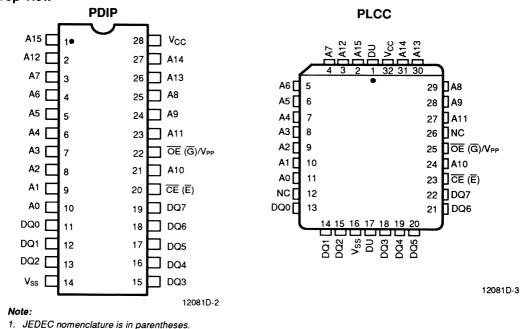

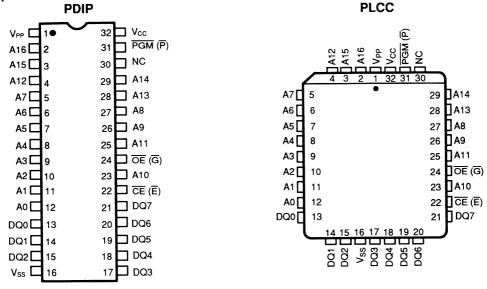

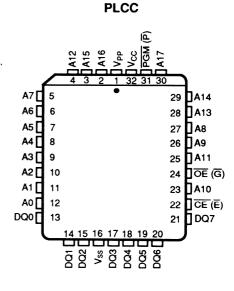

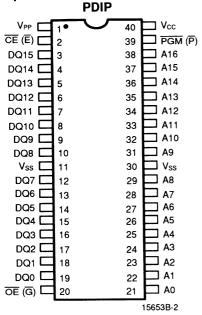

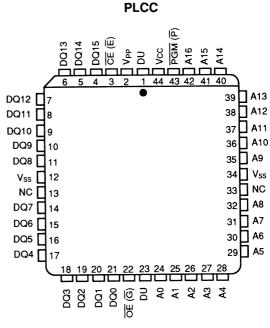

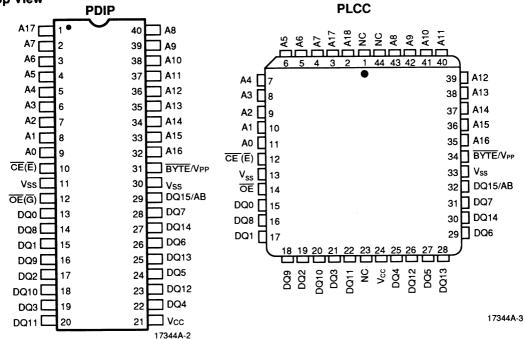

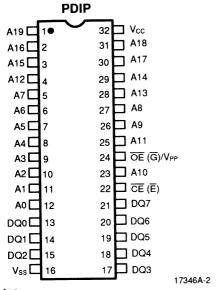

#### **CONNECTION DIAGRAMS**

#### **Top View**

#### Notes:

- 1. JEDEC nomenclature is in parentheses.

- 2. Don't use (DU) for PLCC.

#### **PIN DESIGNATIONS**

A0-A12

= Address Inputs

CE (E)

Chip Enable

DQ0-DQ7

Data Inputs/Outputs

OE (G)

Output Enable Input

PGM (P)

= Program Enable Input

Vcc

V<sub>CC</sub> Supply Voltage

$V_{PP}$

Program Supply Voltage

Vss

= Ground

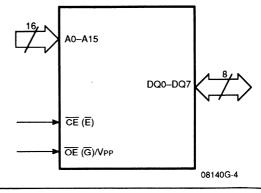

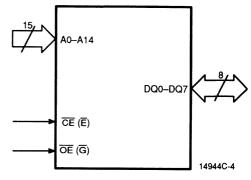

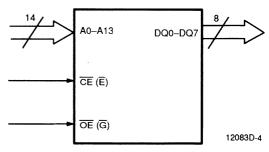

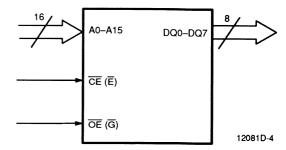

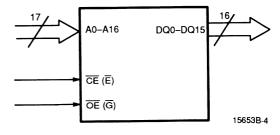

#### LOGIC SYMBOL

11419C-4

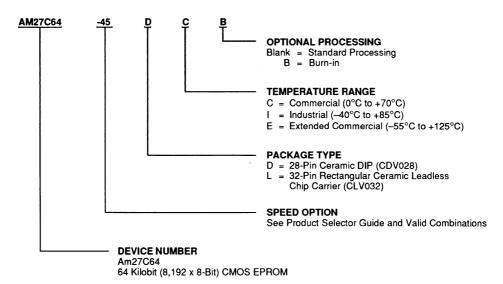

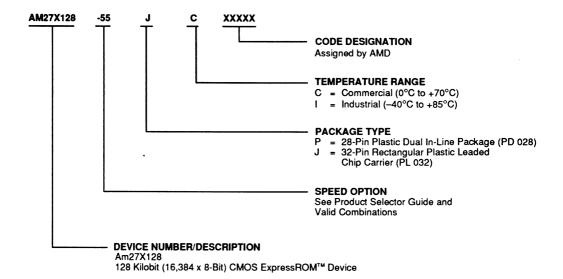

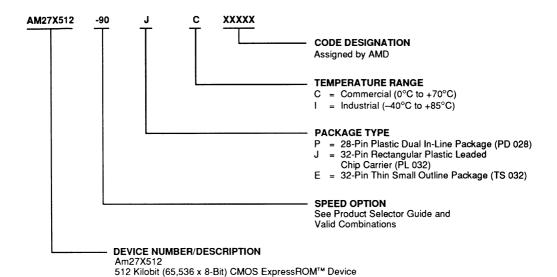

#### **ORDERING INFORMATION**

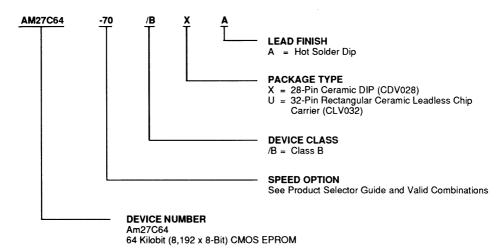

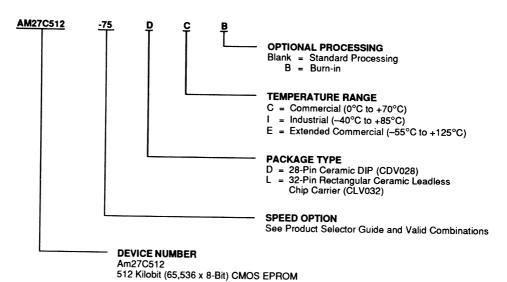

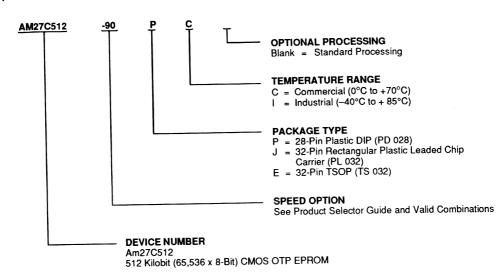

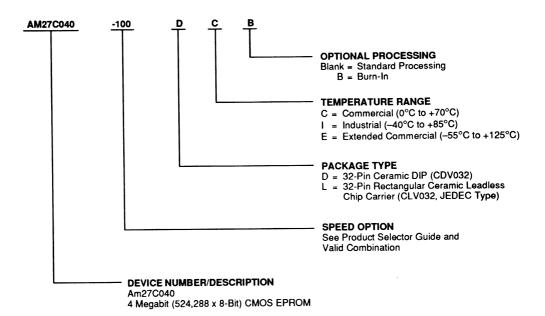

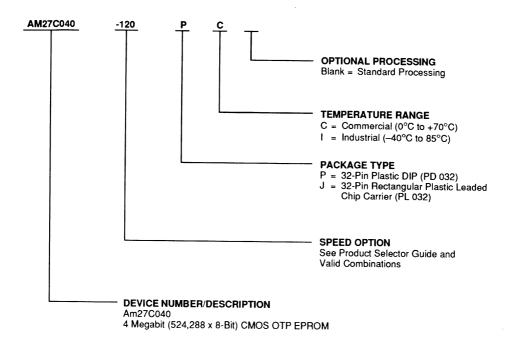

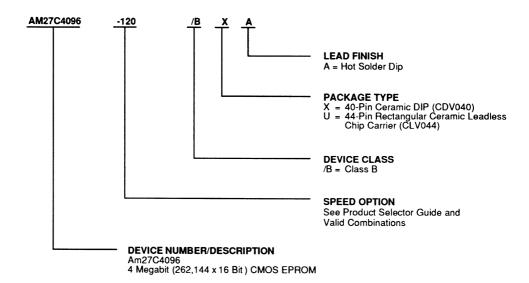

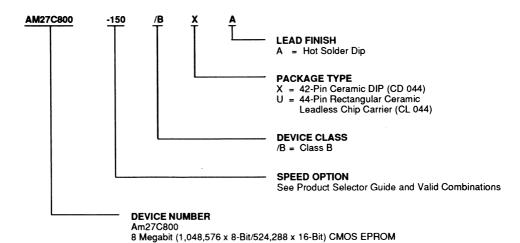

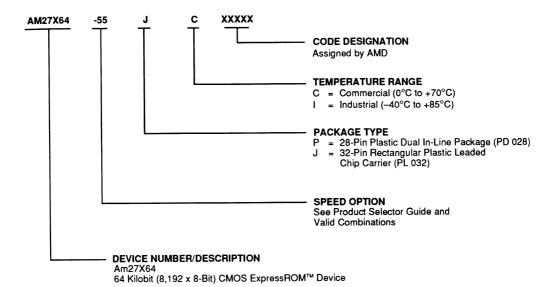

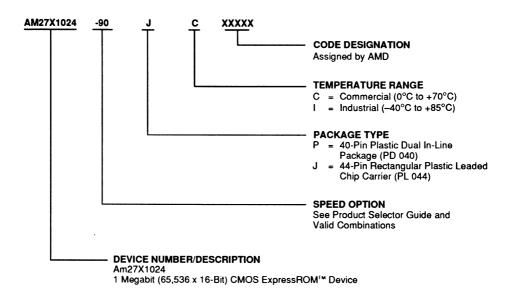

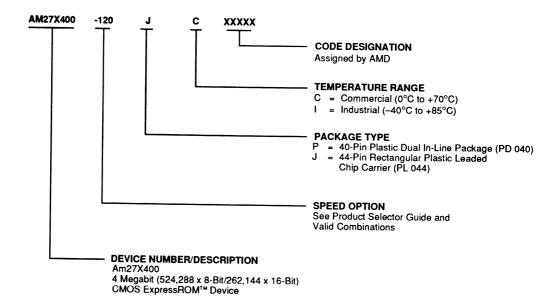

#### **EPROM Products**

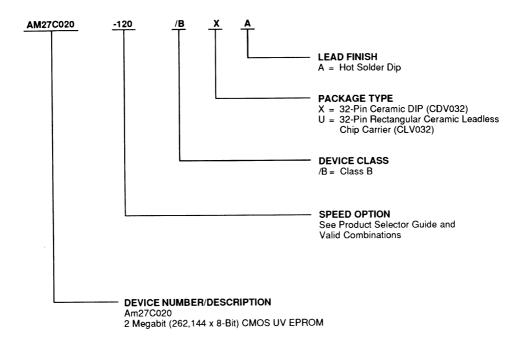

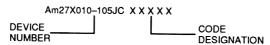

AMD Standard products are available in several packages and operating ranges. The order number (Valid Combination) is formed by a combination of:

| Valid Combinations |                   |  |  |  |  |

|--------------------|-------------------|--|--|--|--|

| AM27C64-45         | DC, DCB, DI, DIB, |  |  |  |  |

| AM27C64-55         | LC, LCB, LI, LIB  |  |  |  |  |

| AM27C64-70         |                   |  |  |  |  |

| AM27C64-90         | DC, DCB, DI,      |  |  |  |  |

| AM27C64-120        | DIB, DE, DEB,     |  |  |  |  |

| AM27C64-150        | LC, LCB, LI,      |  |  |  |  |

| AM27C64-200        | LIB, LE, LEB      |  |  |  |  |

| AM27C64-255        |                   |  |  |  |  |

#### **Valid Combinations**

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations and to check on newly released combinations.

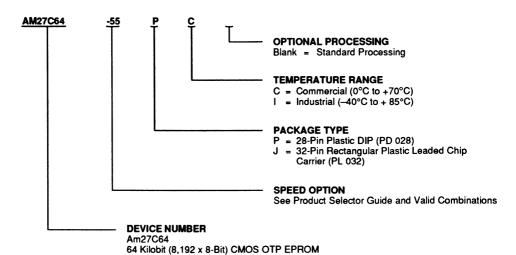

#### **ORDERING INFORMATION**

#### **OTP Products**

AMD Standard products are available in several packages and operating ranges. The order number (Valid Combination) is formed by a combination of:

| Valid Com   | Valid Combinations |  |  |  |  |  |  |  |

|-------------|--------------------|--|--|--|--|--|--|--|

| AM27C64-55  |                    |  |  |  |  |  |  |  |

| AM27C64-70  |                    |  |  |  |  |  |  |  |

| AM27C64-90  | JC. PC.            |  |  |  |  |  |  |  |

| AM27C64-120 | JI. PI.            |  |  |  |  |  |  |  |

| AM27C64-150 | JI, 1º1,           |  |  |  |  |  |  |  |

| AM27C64-200 |                    |  |  |  |  |  |  |  |

| AM27C64-255 |                    |  |  |  |  |  |  |  |

#### **Valid Combinations**

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations and to check on newly released combination.

#### **ORDERING INFORMATION**

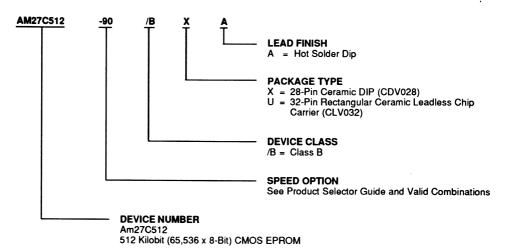

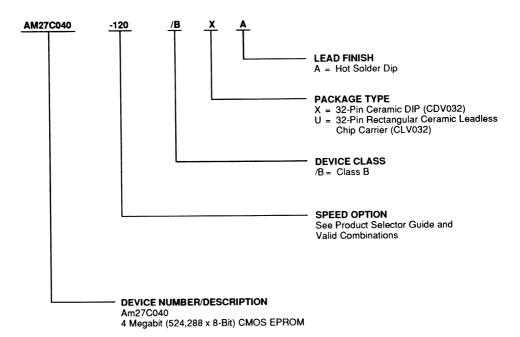

#### Military APL Products

AMD products for Aerospace and Defense applications are available in several packages and operating ranges. APL (Approved Products List) products are fully compliant with MIL-STD-883 requirements. The order number (Valid Combination) is formed by a combination of:

| Valid Combinations |            |  |  |  |  |  |  |

|--------------------|------------|--|--|--|--|--|--|

| AM27C64-70         |            |  |  |  |  |  |  |

| AM27C64-90         |            |  |  |  |  |  |  |

| AM27C64-120        | /BXA, /BUA |  |  |  |  |  |  |

| AM27C64-150        |            |  |  |  |  |  |  |

| AM27C64-200        |            |  |  |  |  |  |  |

#### **Valid Combinations**

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations and to check on newly released combinations.

#### **Group A Tests**

Group A tests consist of Subgroups 1, 2, 3, 7, 8, 9, 10, 11.

#### **FUNCTIONAL DESCRIPTION**

#### Erasing the Am27C64

In order to clear all locations of their programmed contents, it is necessary to expose the Am27C64 to an ultraviolet light source. A dosage of 15 W seconds/cm² is required to completely erase an Am27C64. This dosage can be obtained by exposure to an ultraviolet lamp—wavelength of 2537 Å—with intensity of 12,000  $\mu\text{W/cm}^2$  for 15 to 20 minutes. The Am27C64 should be directly under and about one inch from the source and all filters should be removed from the UV light source prior to erasure.

It is important to note that the Am27C64 and similar devices will erase with light sources having wavelengths shorter than 4000 Å. Although erasure times will be much longer than with UV sources at 2537 Å, exposure to fluorescent light and sunlight will eventually erase the Am27C64 and exposure to them should be prevented to realize maximum system reliability. If used in such an environment, the package window should be covered by an opaque label or substance.

#### **Programming the Am27C64**

Upon delivery or after each erasure the Am27C64 has all 65,536 bits in the "ONE" or HIGH state. "ZEROs" are loaded into the Am27C64 through the procedure of programming.

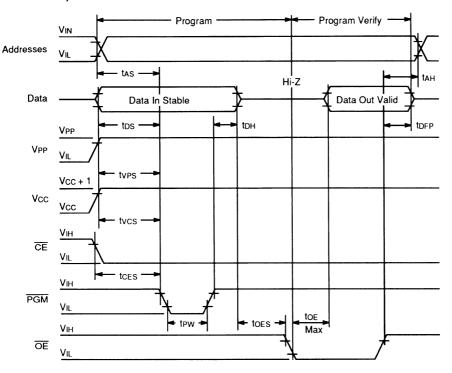

The programming mode is entered when 12.75 V  $\pm$  0.25 V is applied to the V<sub>PP</sub> pin,  $\overline{\text{CE}}$  is at V<sub>IL</sub> and  $\overline{\text{PGM}}$  is at V<sub>II</sub>.

For programming, the data to be programmed is applied 8 bits in parallel to the data output pins.

The Flashrite algorithm reduces programming time by using 100  $\mu$ s programming pulses and by giving each address only as many pulses as is necessary in order to reliably program the data. After each pulse is applied to a given address, the data in that address is verified. If the data does not verify, additional pulses are given until it verifies or the maximum is reached. This process is repeated while sequencing through each address of the Am27C64. This part of the algorithm is done at  $V_{CC}$  = 6.25 V to assure that each EPROM bit is programmed to a sufficiently high threshold voltage. After the final address is completed, the entire EPROM memory is verified at  $V_{CC}$  =  $V_{PP}$  = 5.25 V.

Please refer to Section 6 for programming flow chart and characteristics.

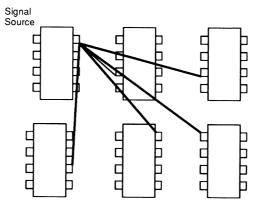

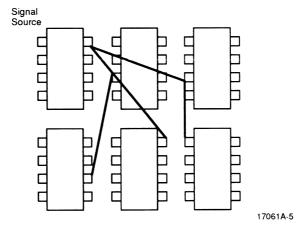

#### **Program Inhibit**

Programming of multiple Am27C64 in parallel with different data is also easily accomplished. Except for  $\overline{CE}$ , all like inputs of the parallel Am27C64 may be common. A TTL low-level program pulse applied to an Am27C64

$\overline{PGM}$  input with V<sub>PP</sub> = 12.75 V ± 0.25 V and  $\overline{CE}$  Low will program that Am27C64. A high-level  $\overline{CE}$  input inhibits the other Am27C64 devices from being programmed.

#### **Program Verify**

A verify should be performed on the programmed bits to determine that they were correctly programmed. The verify should be performed with  $\overline{\text{OE}}$  and  $\overline{\text{CE}}$  at  $V_{\text{IL}}$ ,  $\overline{\text{PGM}}$  at  $V_{\text{IH}}$ , and  $V_{\text{PP}}$  between 12.5 V and 13.0 V.

#### **Auto Select Mode**

The auto select mode allows the reading out of a binary code from an EPROM that will identify its manufacturer and type. This mode is intended for use by programming equipment for the purpose of automatically matching the device to be programmed with its corresponding programming algorithm. This mode is functional in the  $25^{\circ}\text{C} \pm 5^{\circ}\text{C}$  ambient temperature range that is required when programming the Am27C64.

To activate this mode, the programming equipment must force 12.0 V  $\pm$  0.5 V on address line A9 of the Am27C64. Two identifier bytes may then be sequenced from the device outputs by toggling address line A0 from V<sub>IL</sub> to V<sub>IH</sub>. All other address lines must be held at V<sub>IL</sub> during auto select mode.

Byte 0 (A0 =  $V_{IL}$ ) represents the manufacturer code, and byte 1 (A0 =  $V_{IH}$ ), the device code. For the Am27C64, these two identifier bytes are given in the Mode Select Table. All identifiers for manufacturer and device codes will possess odd parity, with the MSB (DQ7) defined as the parity bit.

#### **Read Mode**

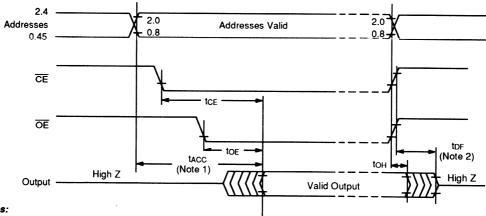

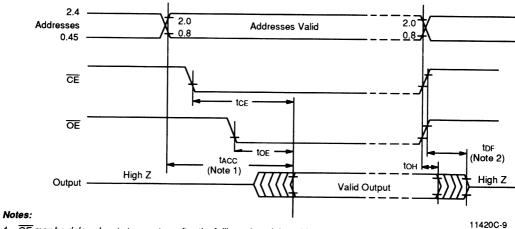

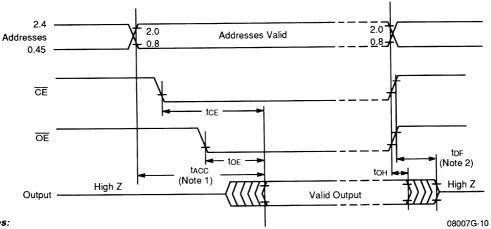

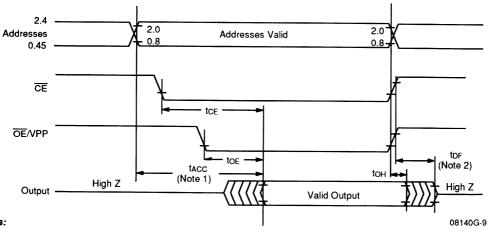

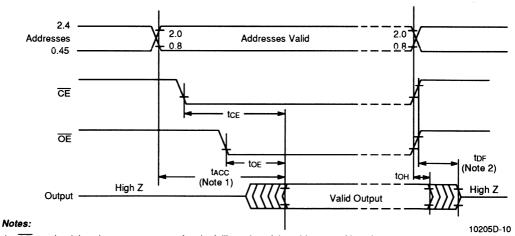

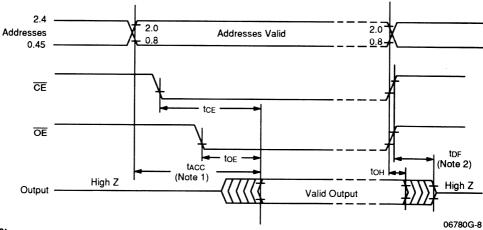

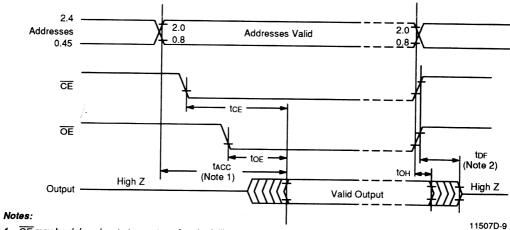

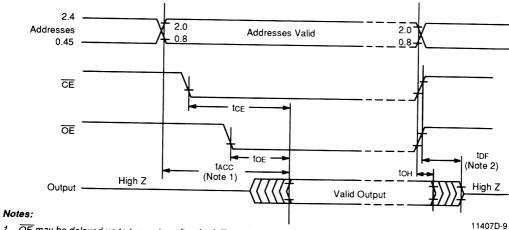

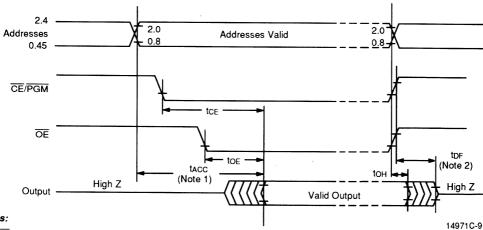

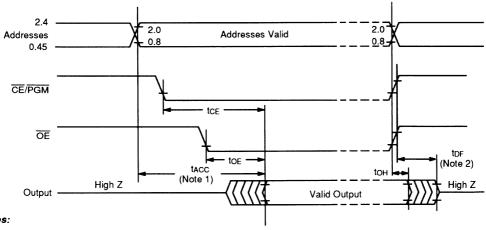

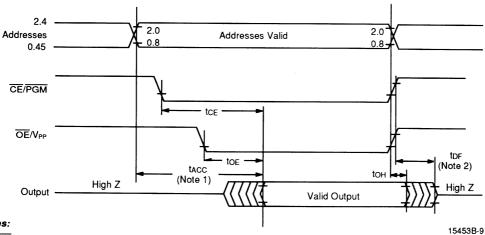

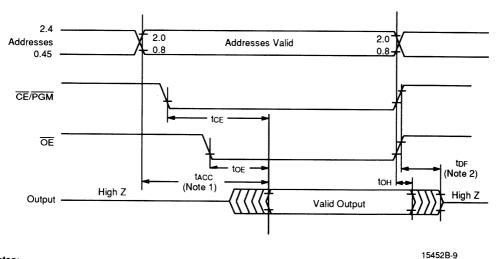

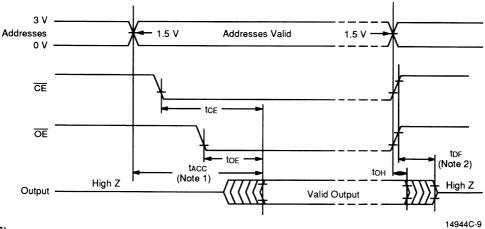

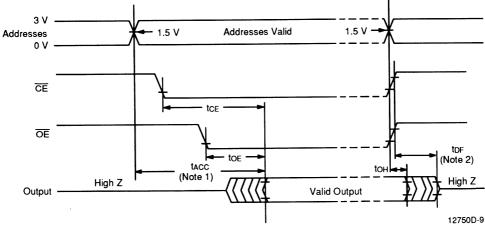

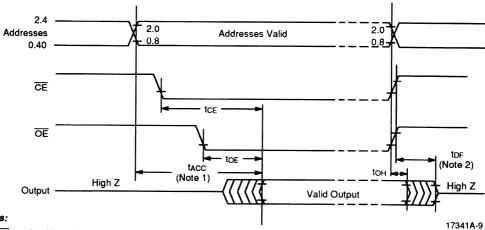

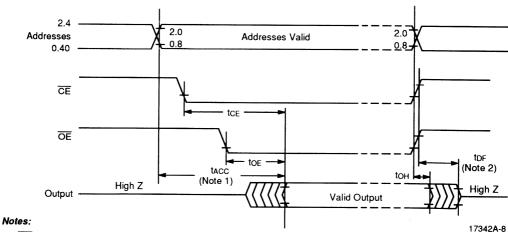

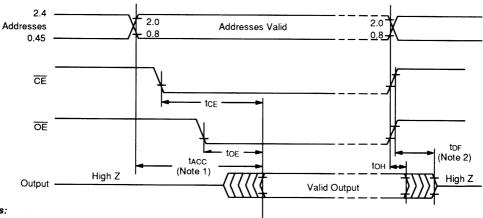

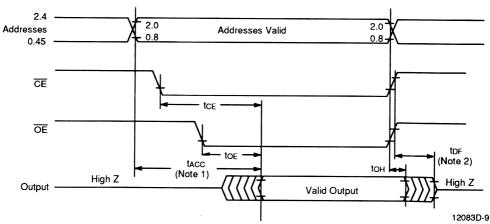

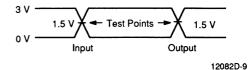

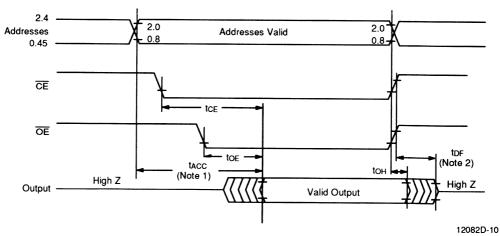

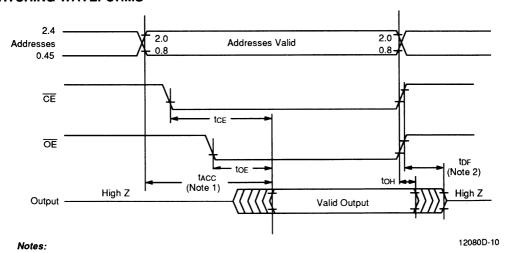

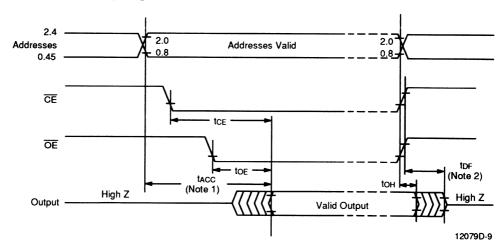

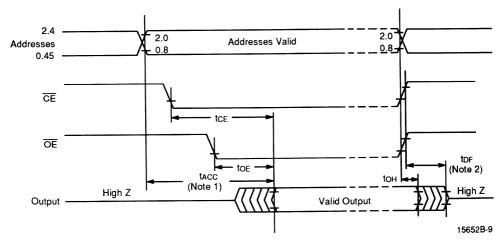

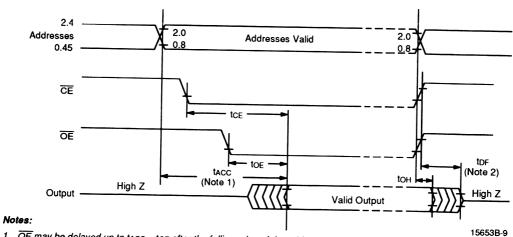

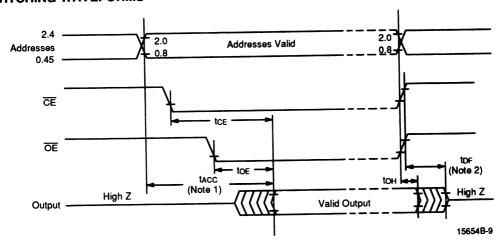

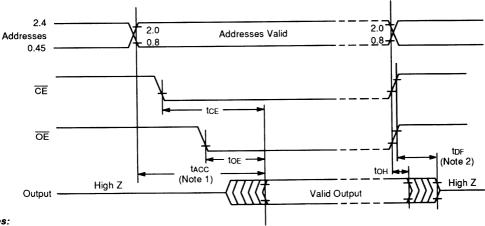

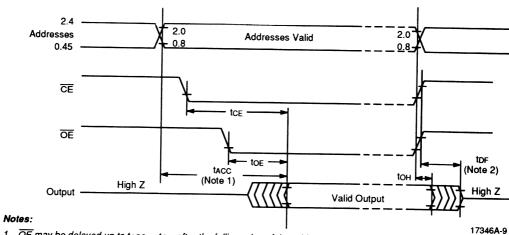

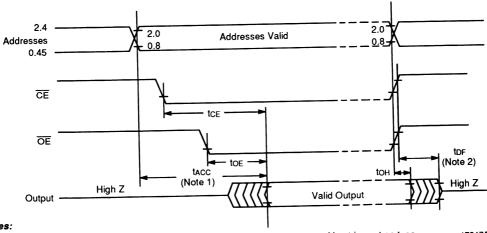

The Am27C64 has two control functions, both of which must be logically satisfied in order to obtain data at the outputs. Chip Enable  $(\overline{CE})$  is the power control and should be used for device selection. Output Enable  $(\overline{OE})$  is the output control and should be used to gate data to the output pins, independent of device selection. Assuming that addresses are stable, address access time (tacc) is equal to the delay from  $\overline{CE}$  to output (tcE). Data is available at the outputs toe after the falling edge of  $\overline{OE}$ , assuming that  $\overline{CE}$  has been LOW and addresses have been stable for at least tacc—toe.

#### Standby Mode

The Am27C64 has a CMOS standby mode which reduces the maximum V<sub>CC</sub> current to 100  $\mu$ A. It is placed in CMOS-standby when  $\overline{\text{CE}}$  is at V<sub>CC</sub>  $\pm$  0.3 V. The Am27C64 also has a TTL-standby mode which reduces the maximum V<sub>CC</sub> current to 1.0 mA. It is placed in TTL-standby when  $\overline{\text{CE}}$  is at V<sub>IH</sub>. When in standby mode, the outputs are in a high-impedance state, independent of the  $\overline{\text{OE}}$  input.

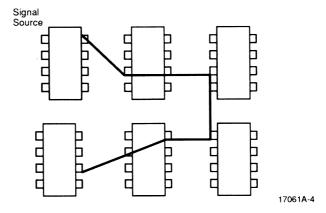

#### **Output OR-Tieing**

To accommodate multiple memory connections, a two-line control function is provided to allow for:

- Low memory power dissipation

- Assurance that output bus contention will not occur

It is recommended that  $\overline{\text{CE}}$  be decoded and used as the primary device-selecting function, while  $\overline{\text{OE}}$  be made a common connection to all devices in the array and connected to the READ line from the system control bus. This assures that all deselected memory devices are in low-power standby mode and that the output pins are only active when data is desired from a particular memory device.

#### System Applications

During the switch between active and standby conditions, transient current peaks are produced on the rising and falling edges of Chip Enable. The magnitude of these transient current peaks is dependent on the output capacitance loading of the device. At a minimum, a 0.1- $\mu F$  ceramic capacitor (high frequency, low inherent inductance) should be used on each device between Vcc and Vss to minimize transient effects. In addition, to overcome the voltage drop caused by the inductive effects of the printed circuit board traces on EPROM arrays, a 4.7- $\mu F$  bulk electrolytic capacitor should be used between Vcc and Vss for each eight devices. The location of the capacitor should be close to where the power supply is connected to the array.

#### **MODE SELECT TABLE**

| Mode                    |                      | CE          | ŌĒ   | PGM | A0  | <b>A</b> 9 | V <sub>PP</sub> | Outputs |

|-------------------------|----------------------|-------------|------|-----|-----|------------|-----------------|---------|

| Read                    |                      | VIL         | VIL  | х   | Х   | Х          | Vcc             | Dout    |

| Output Disable          |                      | Х           | VIH  | Х   | Х   | х          | Vcc             | Hi-Z    |

| Standby (TTL)           |                      | ViH         | Х    | Х   | х   | Х          | Vcc             | Hi-Z    |

| Standby (CMOS)          |                      | Vcc ± 0.3 V | Х    | Х   | Х   | Х          | Vcc             | Hi-Z    |

| Program                 | Program              |             | Х    | VIL | Х   | Х          | Vpp             | Din     |

| Program Verify          | VIL VIL VIH X X VPP  |             | Dоит |     |     |            |                 |         |

| Program Inhibit         |                      | Vıн         | Х    | Х   | Х   | Х          | Vpp             | Hi-Z    |

| Auto Select<br>(Note 3) | Manufacturer<br>Code | VIL         | VIL  | х   | VIL | Vн         | Vcc             | 01H     |

|                         | Device Code          | VIL         | VIL  | Х   | ViH | Vн         | Vcc             | 15H     |

#### Notes:

- 1.  $V_H = 12.0 V \pm 0.5 V$

- 2.  $X = Either V_{IH}$  or  $V_{IL}$

- 3.  $A1-A8 = A10-A12 = V_{IL}$

- 4. See DC Programming Characteristics for VPP voltage during programming.

#### **ABSOLUTE MAXIMUM RATINGS**

| Storage Temperature         OTP Products         -65°C to +125°C           All Other Products         -65°C to +150°C |

|-----------------------------------------------------------------------------------------------------------------------|

| Ambient Temperature with Power Applied55°C to +125°C                                                                  |

| Voltage with Respect To Vss $$ All pins except A9,VPP,VCC $$ . $$ –0.6 V to Vcc + 0.5 V $$                            |

| A9 and V <sub>PP</sub> 0.6 V to +13.5 V                                                                               |

| Vcc0.6 V to +7.0 V                                                                                                    |

#### Notes:

- Minimum DC voltage on input or I/O pins is -0.5 V. During transitions, the inputs may overshoot Vss to -2.0 V for periods of up to 20 ns. Maximum DC voltage on input and I/O pins is Vcc + 0.5 V which may overshoot to Vcc + 2.0 V for periods up to 20 ns.

- For A9 and V<sub>PP</sub> the minimum DC input is -0.5 V. During transitions, A9 and V<sub>PP</sub> may overshoot V<sub>SS</sub> to -2.0 V for periods of up to 20 ns. A9 and V<sub>PP</sub> must not exceed 13.5 V for any period of time.